Medalist 17242, 13032, 10232, 8422 and 4312, Rev. A 23

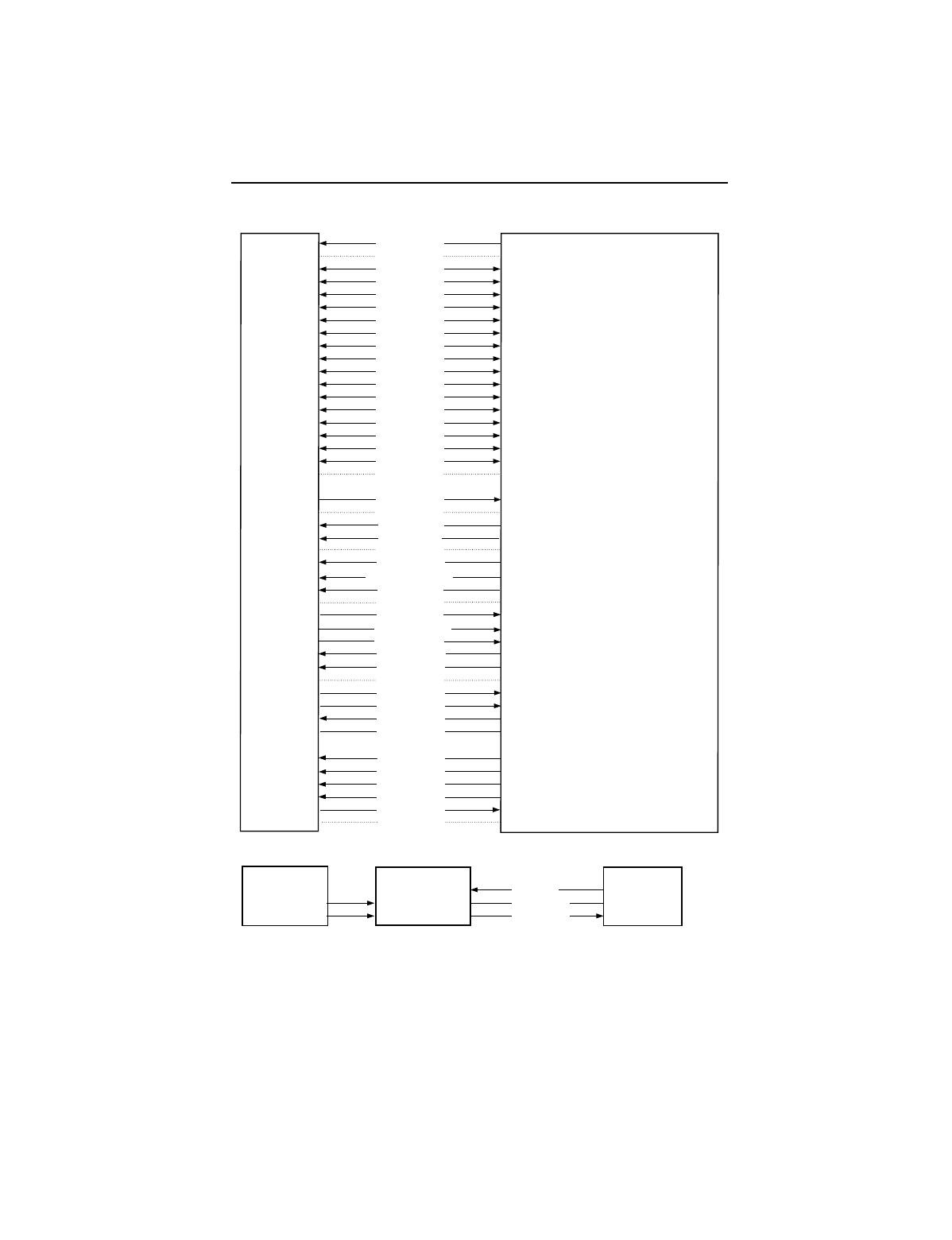

Figure 4. I/O pins and supported ATA signals

Reset

–

Ground

DD7

DD8

DD6

DD9

DD5

DD10

DD4

DD11

DD3

DD12

DD2

DD13

DD1

DD14

DD0

DD15

Ground

(removed)

DMARQ

Ground

DIOW–

STOP

Ground

DIOR

–

HDMARDY

–

HSTROBE

Ground

IORDY

DDMARDY–

DSTROBE

CSEL

DMACK

–

Ground

INTRQ

IOCS16

–

DA1

PDIAG

–

CBLID–

DA0

DA2

CS0

–

CS1

–

DASP

–

Ground

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

Hardware Reset

Ground

Host Data Bus Bit 7

Host Data Bus Bit 8

Host Data Bus Bit 6

Host Data Bus Bit 9

Host Data Bus Bit 5

Host Data Bus Bit 10

Host Data Bus Bit 4

Host Data Bus Bit 11

Host Data Bus Bit 3

Host Data Bus Bit 12

Host Data Bus Bit 2

Host Data Bus Bit 13

Host Data Bus Bit 1

Host Data Bus Bit 14

Host Data Bus Bit 0

Device Data (15:0)

Ground

(No Pin)

DMA Request

Ground

Device I/O Write:

Stop Ultra DMA Burst

Ground

Device I/O Read:

Host Ultra DMA Ready:

Host Ultra DMA Data Strobe

Ground

I/O Channel Ready

Device Ultra DMA Ready

Device Ulta DMA Data Strobe

Cable Select

DMA Acknowledge

Ground

Device Interrupt

Reserved

Host Address Bus Bit 1

Passed Diagnostics

Cable Assembly Type Identifier

Device Address (2:0)

Device Address (2:0)

Chip Select (1:0)

Chip Select (1:0)

Drive Active/Slave Present

Ground

Host pin # and signal description

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

Drive pin #

Signal name

Pins 28, 34 and 39 are used for master-slave communication (details shown below).

Host

28

34

39

Drive 0 (master)Drive 1 (slave)

28

34

39

28

34

39

CSEL

PDIAG

–

DASP–