LAN9118 Family Programmer Reference Guide

SMSC AN 12.12 25 Revision 1.0 (12-14-09)

APPLICATION NOTE

Step Three:

Keep reading the MAC_CSR_CMD Register until the CSR Busy Bit =0.

Load the MII write command word (MII W/nR == 1) that is to be written to the MII ACC register into

the MAC_CSR_Data register. The command word will write the contents of the MII DATA register to

the PHY Advertisement register (0x4) (note that the lighter-shaded heading is expressed in MII ACC

register terms).

Step Four:

Write the command word into the MAC_CSR_CMD register. This causes the MII ACC register (0x06)

to be written (R/nW == 0) with the contents of the MAC_CSR_Data register, which in turn causes the

MII register write to be executed.

Steps 5-8:

5. Read the MAC_CSR_CMD Register until the Busy Bit = 0.

6. Load the MAC_CSR_CMD Register as follows: CSR Busy = 1, R/nW = 1 (Read), CSR Address

= 0x06 (MII_ACC Register)

7. Read the MAC_CSR_CMD Register until the Busy Bit = 0

8. Read the MAC_CSR_DATA Register. Repeat steps 6-8 until the MII Busy Bit (Bit 0) = 0.

Example 2: Read the PHY Status register (register 1)

Step One:

Load the MAC_CSR_Data register with the MII ACC register command word to read (MII W/nR == 1)

PHY register 1 (MII Register == 1). Note that the lighter-shaded heading is expressed in MII ACC

terms.

Step Two:

Write the command word into the MAC_CSR_CMD register. This causes the contents of the

MAC_CSR_Data register to be written (R/nW == 0) to the MII ACC register (0x06), which executes

the PHY read. The resulting read from the PHY is then loaded to the MII Data register

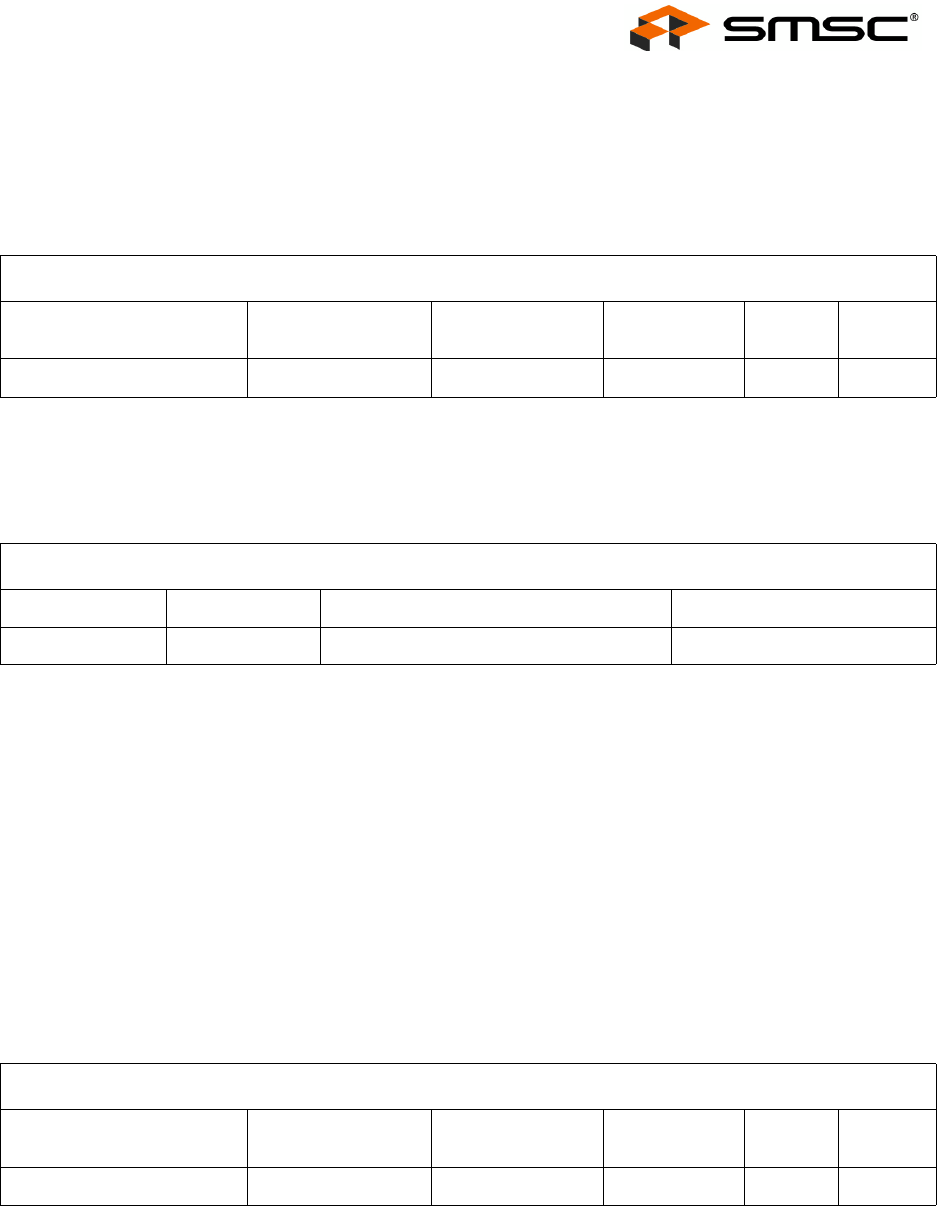

MAC_CSR_DATA (TO BE LOADED INTO MII ACC REGISTER)

Reserved

(31:16)

PHY Address

(15:11)

MII Register

(10:6)

Reserved

(5:2)

MII

W/nR

MII

Busy

0x1 0x4 1 1

MAC_CSR_CMD (ACCESSING MII_ACC REGISTER)

CSR Busy R/nW Reserved (29:8) CSR Address (7:0)

1 0 0x06

MAC_CSR_DATA

Reserved

(31:16)

PHY Address

(15:11)

MII Register

(10:6)

Reserved

(5:2)

MII

W/nR

MII

Busy

0x1 0x1 0 1