MII/RMII 10/100 Ethernet Transceiver with HP Auto-MDIX and flexPWR

®

Technology in a Small Footprint

Datasheet

Revision 1.0 (04-15-09) 24 SMSC LAN8710/LAN8710i

DATASHEET

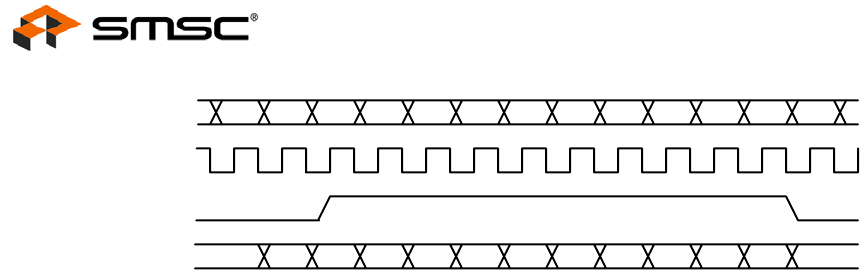

Figure 4.3 Relationship Between Received Data and Specific MII Signals

4.3.8 Receiver Errors

During a frame, unexpected code-groups are considered receive errors. Expected code groups are the

DATA set (0 through F), and the /T/R/ (ESD) symbol pair. When a receive error occurs, the RXER

signal is asserted and arbitrary data is driven onto the RXD[3:0] lines. Should an error be detected

during the time that the /J/K/ delimiter is being decoded (bad SSD error), RXER is asserted true and

the value ‘1110’ is driven onto the RXD[3:0] lines. Note that the Valid Data signal is not yet asserted

when the bad SSD error occurs.

4.3.9 100M Receive Data Across the MII/RMII Interface

In MII mode, the 4-bit data nibbles are sent to the MII block. These data nibbles are clocked to the

controller at a rate of 25MHz. The controller samples the data on the rising edge of RXCLK. To ensure

that the setup and hold requirements are met, the nibbles are clocked out of the transceiver on the

falling edge of RXCLK. RXCLK is the 25MHz output clock for the MII bus. It is recovered from the

received data to clock the RXD bus. If there is no received signal, it is derived from the system

reference clock (XTAL1/CLKIN).

When tracking the received data, RXCLK has a maximum jitter of 0.8ns (provided that the jitter of the

input clock, XTAL1/CLKIN, is below 100ps).

In RMII mode, the 2-bit data nibbles are sent to the RMII block. These data nibbles are clocked to the

controller at a rate of 50MHz. The controller samples the data on the rising edge of XTAL1/CLKIN

(REF_CLK). To ensure that the setup and hold requirements are met, the nibbles are clocked out of

the transceiver on the falling edge of XTAL1/CLKIN (REF_CLK).

4.4 10Base-T Transmit

Data to be transmitted comes from the MAC layer controller. The 10Base-T transmitter receives 4-bit

nibbles from the MII at a rate of 2.5MHz and converts them to a 10Mbps serial data stream. The data

stream is then Manchester-encoded and sent to the analog transmitter, which drives a signal onto the

twisted pair via the external magnetics.

The 10M transmitter uses the following blocks:

MII (digital)

TX 10M (digital)

10M Transmitter (analog)

10M PLL (analog)

4.4.1 10M Transmit Data Across the MII/RMII Interface

The MAC controller drives the transmit data onto the TXD BUS. For MII, when the controller has driven

TXEN high to indicate valid data, the data is latched by the MII block on the rising edge of TXCLK.

The data is in the form of 4-bit wide 2.5MHz data.

5D5 data data data data

RXD

RX_DV

RX_CLK

5D5

data data data data

CLEAR-TEXT

5JK

5 55

TR

Idle