MII/RMII 10/100 Ethernet Transceiver with HP Auto-MDIX and flexPWR

®

Technology in a Small Footprint

Datasheet

Revision 1.0 (04-15-09) 70 SMSC LAN8710/LAN8710i

DATASHEET

Note 7.3 These levels apply when a 0-3.3V Clock is driven into XTAL1/CLKIN and XTAL2 is floating.

The maximum input voltage on XTAL1/CLKIN is VDD2A + 0.4V.

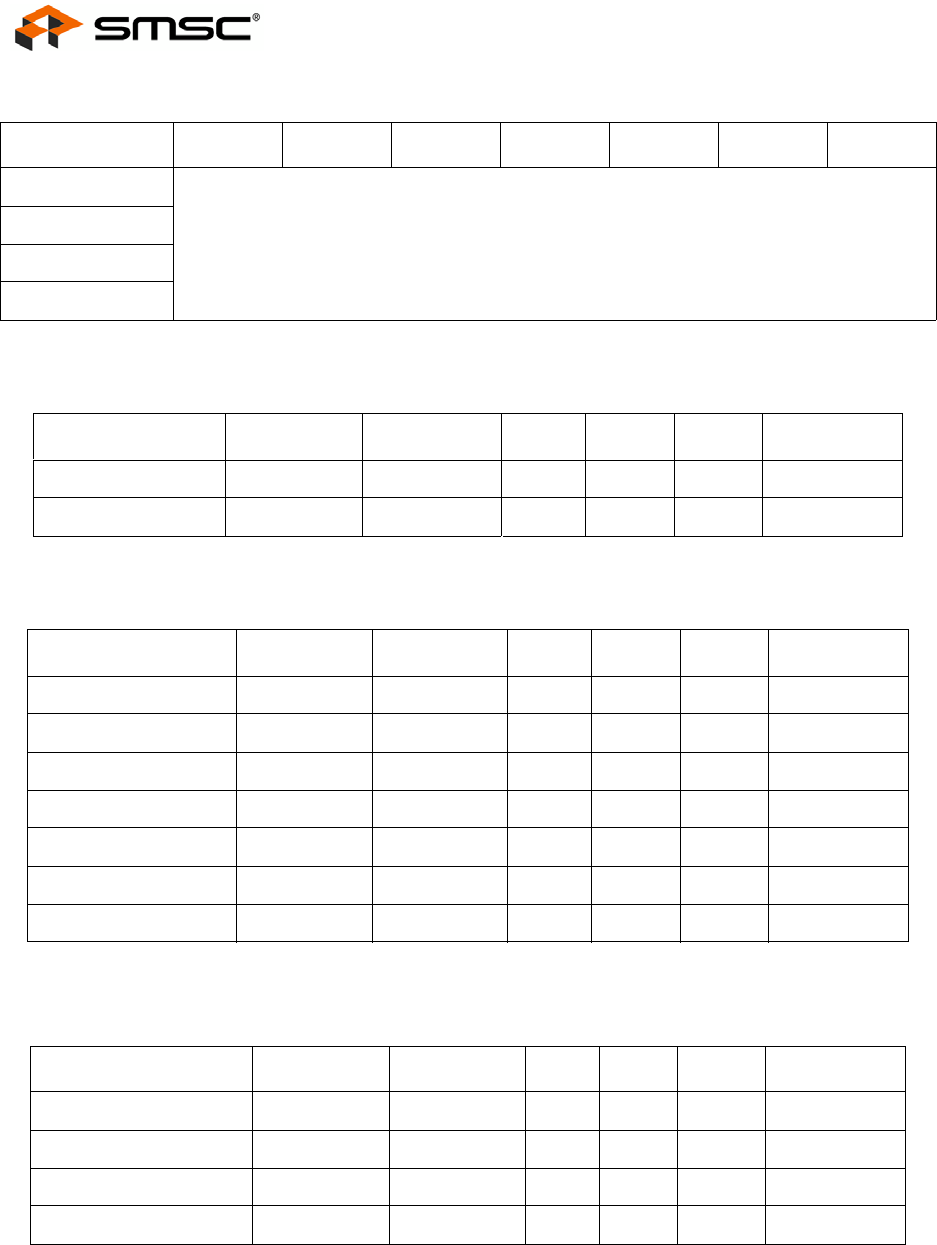

Table 7.6 LAN Interface Signals

NAME V

IH

V

IL

I

OH

I

OL

V

OL

V

OH

TXP

See Table 7.11, “100Base-TX Transceiver Characteristics,” on page 71 and Table 7.12,

“10BASE-T Transceiver Characteristics,” on page 72.

TXN

RXP

RXN

Table 7.7 LED Signals

NAME V

IH

(V) V

IL

(V) I

OH

I

OL

V

OL

(V) V

OH

(V)

LED1/REGOFF 0.63 * VDD2A 0.39 * VDD2A -12 mA +12 mA +0.4 VDD2A – +0.4

LED2/nINTSEL 0.63 * VDD2A 0.39 * VDD2A -12 mA +12 mA +0.4 VDD2A – +0.4

Table 7.8 Configuration Inputs

NAME V

IH

(V) V

IL

(V) I

OH

I

OL

V

OL

(V) V

OH

(V)

RXD0/MODE0 0.63 * VDDIO 0.39 * VDDIO -8 mA +8 mA +0.4 VDDIO – +0.4

RXD1/MODE1 0.63 * VDDIO 0.39 * VDDIO -8 mA +8 mA +0.4 VDDIO – +0.4

RXD2/RMIISEL 0.63 * VDDIO 0.39 * VDDIO -8 mA +8 mA +0.4 VDDIO – +0.4

RXD3/PHYAD2 0.63 * VDDIO 0.39 * VDDIO -8 mA +8 mA +0.4 VDDIO – +0.4

RXER/RXD4/PHYAD0 0.63 * VDDIO 0.39 * VDDIO -8 mA +8 mA +0.4 VDDIO – +0.4

RXCLK/PHYAD1 0.63 * VDDIO 0.39 * VDDIO -8 mA +8 mA +0.4 VDDIO – +0.4

COL/CRS_DV/MODE2 0.63 * VDDIO 0.39 * VDDIO -8 mA +8 mA +0.4 VDDIO – +0.4

Table 7.9 General Signals

NAME V

IH

(V) V

IL

(V) I

OH

I

OL

V

OL

(V) V

OH

(V)

nINT/TXER/TXD4 -8 mA +8 mA +0.4 VDDIO – +0.4

nRST 0.63 * VDDIO 0.39 * VDDIO

XTAL1/CLKIN (Note 7.3) +1.40 V 0.39 * VDD2A

XTAL2 - -