MII/RMII 10/100 Ethernet Transceiver with HP Auto-MDIX and flexPWR

®

Technology in a Small Footprint

Datasheet

SMSC LAN8710/LAN8710i 53 Revision 1.0 (04-15-09)

DATASHEET

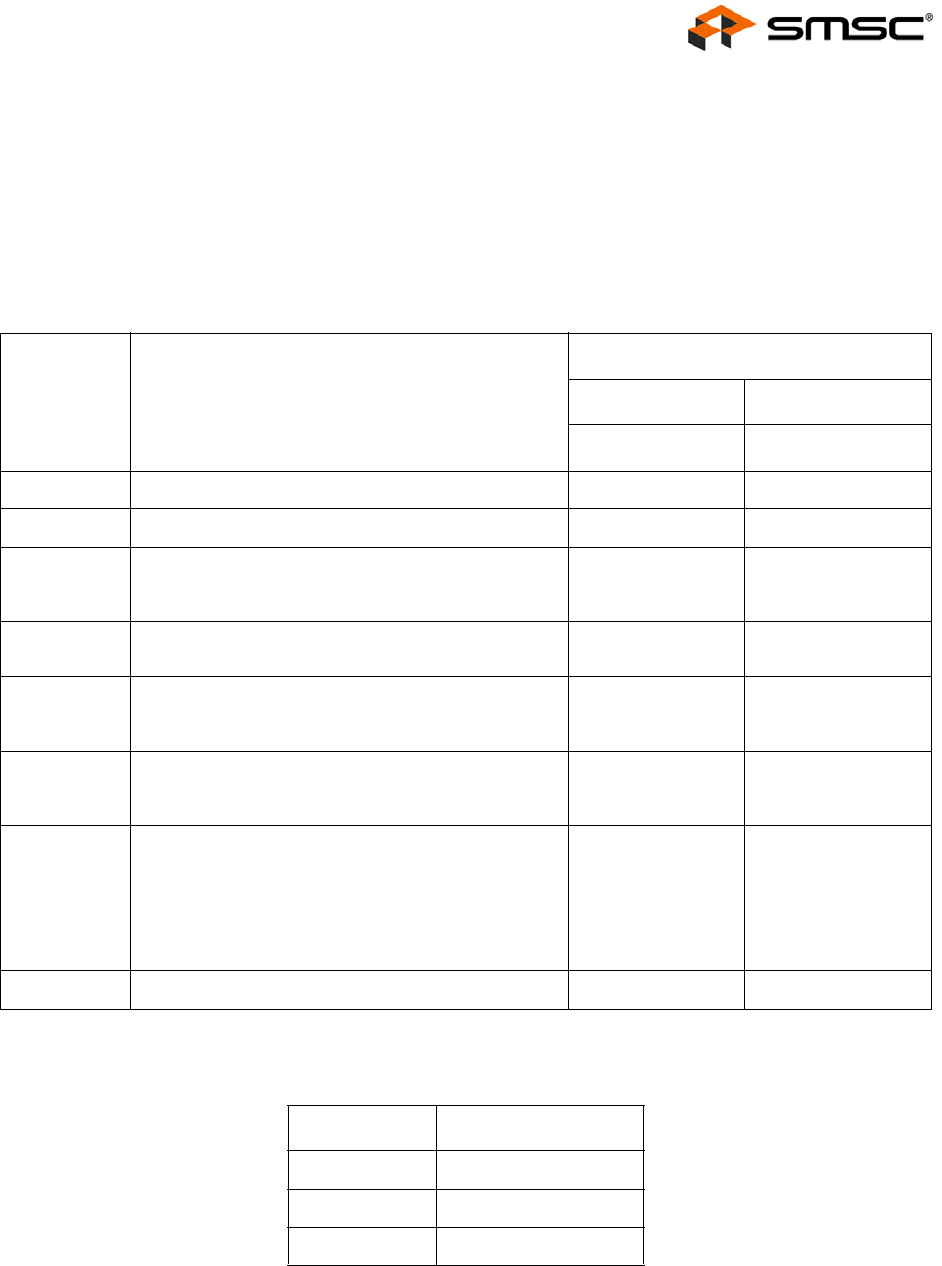

5.3.9.2 Mode Bus – MODE[2:0]

The MODE[2:0] bus controls the configuration of the 10/100 digital block. When the nRST pin is

deasserted, the register bit values are loaded according to the MODE[2:0] pins. The 10/100 digital

block is then configured by the register bit values. When a soft reset occurs (bit 0.15) as described in

Table 5.21, the configuration of the 10/100 digital block is controlled by the register bit values, and the

MODE[2:0] pins have no affect.

The LAN8710 mode may be configured using hardware configuration as summarized in Table 5.40.

The user may configure the transceiver mode by writing the SMI registers.

The MODE[2:0] hardware configuration pins are multiplexed with other signals as shown in Table 5.41.

5.3.9.3 MII/RMII Mode Selection

MII or RMII mode selection is latched on the rising edge of the internal reset (nRESET) based on the

strapping of the RXD2/RMIISEL pin. The default mode is MII with the internal pull-down resistor. To

select RMII mode, pull the RXD2/RMIISEL pin high with an external resistor to VDDIO.

Table 5.40 MODE[2:0] Bus

MODE[2:0] MODE DEFINITIONS

DEFAULT REGISTER BIT VALUES

REGISTER 0 REGISTER 4

[13,12,10,8] [8,7,6,5]

000 10Base-T Half Duplex. Auto-negotiation disabled. 0000 N/A

001 10Base-T Full Duplex. Auto-negotiation disabled. 0001 N/A

010 100Base-TX Half Duplex. Auto-negotiation

disabled.

CRS is active during Transmit & Receive.

1000 N/A

011 100Base-TX Full Duplex. Auto-negotiation disabled.

CRS is active during Receive.

1001 N/A

100 100Base-TX Half Duplex is advertised. Auto-

negotiation enabled.

CRS is active during Transmit & Receive.

1100 0100

101 Repeater mode. Auto-negotiation enabled.

100Base-TX Half Duplex is advertised.

CRS is active during Receive.

1100 0100

110 Power Down mode. In this mode the transceiver will

wake-up in Power-Down mode. The transceiver

cannot be used when the MODE[2:0] bits are set to

this mode. To exit this mode, the MODE bits in

Register 18.7:5(see Table 5.30) must be configured

to some other value and a soft reset must be

issued.

N/A N/A

111 All capable. Auto-negotiation enabled. X10X 1111

Table 5.41 Pin Names for Mode Bits

MODE BIT PIN NAME

MODE[0] RXD0/MODE0

MODE[1] RXD1/MODE1

MODE[2] COL/CRS_DV/MODE2