15

Th

e

Ult

ra

SPARC

T

2

P

rocessor w

ith

C

oo

lTh

rea

d

s

T

ec

h

no

l

ogy

Sun Microsystems, Inc.

3DES, AES, RC4, SHA-1, SHA-256, MD5, RSA to 2048 key, ECC, and CRC32. Embedding

hardware cryptographic acceleration for these ciphers allows end-to-end encryption

with no penalty in either performance or cost.

UltraSPARC T2 Core Architecture and Pipelines

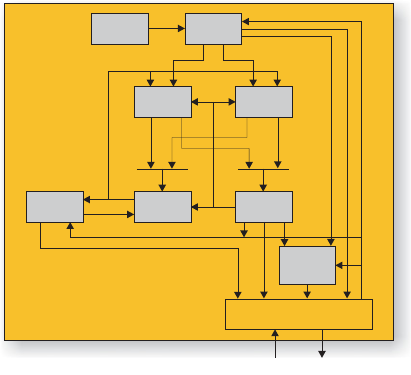

Figure 6 provides a block-level diagram representing a single UltraSPARC cores on the

UltraSPARC T2 processor (up to eight are supported per processor).

Figure 6. UltraSPARC T2 core block diagram

Components implemented in each core include:

•

Trap Logic Unit (TLU)

— The trap logic unit updates the machine state as well as

handling exceptions and interrupts.

•

Instruction Fetch Unit (IFU)

— The instruction fetch unit includes the 16KB

instruction cache (32-byte lines, 8-way set associative) and a 64-entry fully-associative

instruction translation lookup buffer (ITLB).

•

Integer Execution Units (EXU)

— Dual integer execution units are provided per core

with four threads sharing each unit. Eight register windows are provided per thread,

with 160 integer register file (IRF) entries per thread.

•

Floating Point/Graphics Unit (FGU)

— A floating point/graphics unit is provided

within each core and it is shared by all eight threads assigned to the core. 32 floating-

point register file entries are provided per thread.

•

Stream Processing Unit (SPU)

— Each core contains a stream processing unit that

provides cryptographic coprocessing.

•

Memory Management Unit (MMU)

— The memory management unit provides a

hardware table walk (HWTW) and supports 8 KB, 64 KB, 4 MB, and 256 MB pages.

IFU

EXU0 EXU1

SPU FGU LSU

MMU/

HWTW

Gasket

TLU

Crossbar / L2 Cache

UltraSPARC T2 core