www.ti.com

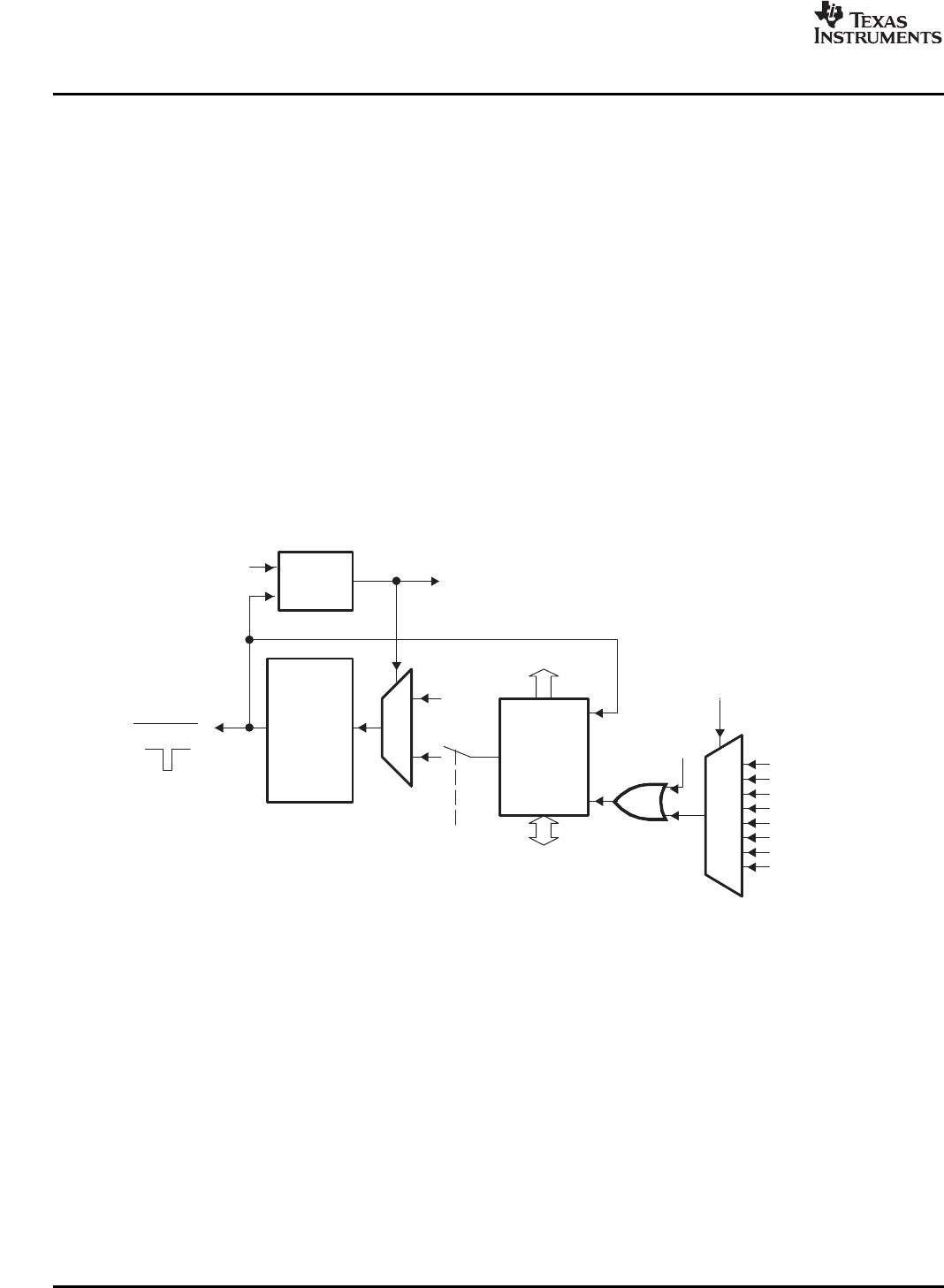

Latch

Generate

interrupt

pulse

when

input = 1

2-bit

Counter

Set

Clear

1

0

0

Clear CNT

Inc CNT

ETPS[INTCNT]

ETPS[INTPRD]

ETCLR[INT]

EPWMxINT

ETFRC[INT]

ETSEL[INT]

ETFLG[INT]

ETSEL[INTSEL]

000

001

010

011

100

101

111

101

0

0

CTRU=CMPA

CTRD=CMPA

CTRU=CMPB

CTRD=CMPB

CTR=Zero

CTR=PRD

Event-Trigger(ET)Submodule

Thenumberofeventsthathaveoccurredcanbereadfromtheinterrupteventcounter(ETPS[INTCNT])

registerbits.Thatis,whenthespecifiedeventoccurstheETPS[INTCNT]bitsareincrementeduntilthey

reachthevaluespecifiedbyETPS[INTPRD].WhenETPS[INTCNT]=ETPS[INTPRD]thecounterstops

countinganditsoutputisset.ThecounterisonlyclearedwhenaninterruptissenttothePIE.

WhenETPS[INTCNT]reachesETPS[INTPRD]theoneofthefollowingbehaviorswilloccur:

•Ifinterruptsareenabled,ETSEL[INTEN]=1andtheinterruptflagisclear,ETFLG[INT]=0,thenan

interruptpulseisgeneratedandtheinterruptflagisset,ETFLG[INT]=1,andtheeventcounteris

clearedETPS[INTCNT]=0.Thecounterwillbegincountingeventsagain.

•Ifinterruptsaredisabled,ETSEL[INTEN]=0,ortheinterruptflagisset,ETFLG[INT]=1,thecounter

stopscountingeventswhenitreachestheperiodvalueETPS[INTCNT]=ETPS[INTPRD].

•Ifinterruptsareenabled,buttheinterruptflagisalreadyset,thenthecounterwillholditsoutputhigh

untiltheENTFLG[INT]flagiscleared.Thisallowsforoneinterrupttobependingwhileoneisserviced.

WritingtotheINTPRDbitswillautomaticallyclearthecounterINTCNT=0andthecounteroutputwillbe

reset(sonointerruptsaregenerated).Writinga1totheETFRC[INT]bitwillincrementtheeventcounter

INTCNT.ThecounterwillbehaveasdescribedabovewhenINTCNT=INTPRD.WhenINTPRD=0,the

counterisdisabledandhencenoeventswillbedetectedandtheETFRC[INT]bitisalsoignored.

Theabovedefinitionmeansthatyoucangenerateaninterruptoneveryevent,oneverysecondevent,or

oneverythirdevent.Aninterruptcannotbegeneratedoneveryfourthormoreevents.

Figure2-41.Event-TriggerInterruptGenerator

Figure2-42showstheoperationoftheevent-trigger'sstart-of-conversion-A(SOCA)pulsegenerator.The

ETPS[SOCACNT]counterandETPS[SOCAPRD]periodvaluesbehavesimilarlytotheinterruptgenerator

exceptthatthepulsesarecontinuouslygenerated.Thatis,thepulseflagETFLG[SOCA]islatchedwhena

pulseisgenerated,butitdoesnotstopfurtherpulsegeneration.Theenable/disablebitETSEL[SOCAEN]

stopspulsegeneration,butinputeventscanstillbecounteduntiltheperiodvalueisreachedaswiththe

interruptgenerationlogic.TheeventthatwilltriggeranSOCAandSOCBpulsecanbeconfigured

separatelyintheETSEL[SOCASEL]andETSEL[SOCBSEL]bits.Thepossibleeventsarethesame

eventsthatcanbespecifiedfortheinterruptgenerationlogic.

66ePWMSubmodulesSPRU791D–November2004–RevisedOctober2007

SubmitDocumentationFeedback