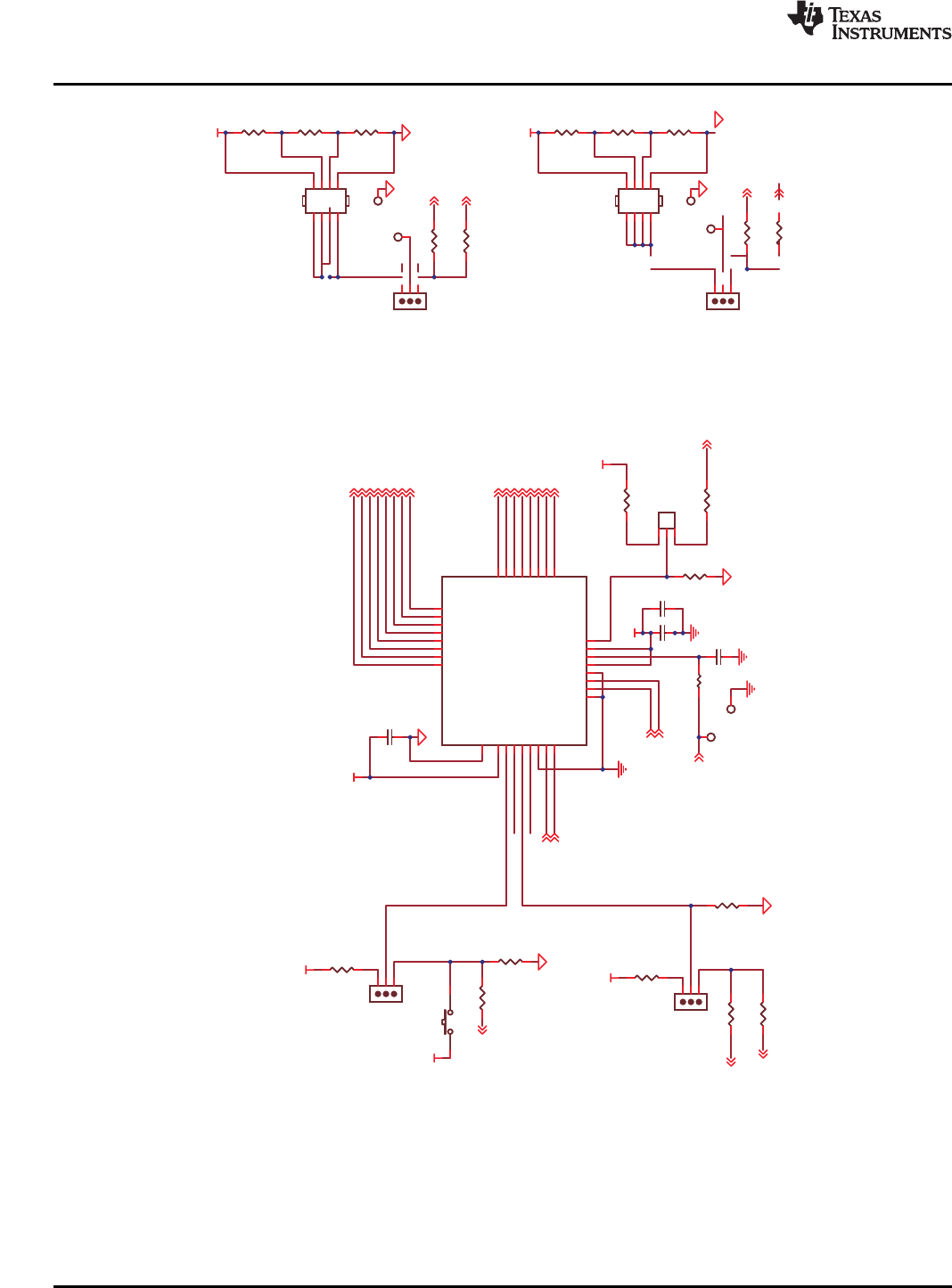

ICLKP

ICLKM

SEN

SDA

SCLOCK

PDWN

SEN

RESET

SCLOCK

+3.3VD

+3.3VA

+3.3VD

+3.3VD

+3.3VD

+3.3VD

+3.3VD

+3.3VD

IN_M

SH1

IN_P

SH1

D2_D3_P SH4

D0_D1_P SH4

D0_D1_M SH4

D2_D3_M SH4

D4_D5_P SH4

D4_D5_M

SH4

D6_D7_P SH4

D6_D7_M

SH4

ICLKP

SH3

ICLKM

SH3

ADCRESETSH5

SDATASH5

VREF

SH1

PDN SH5

CS SH5

SCLK SH5

FPGA_SEN SH4

FPGA_SCLK SH4

FPGA_SDATASH4

CLKOUTP

SH4

CLKOUTM

SH4

D8_D9_P

SH4

D8_D9_M

SH4

D10_D11_P

SH4

D10_D1

1_M

SH4

D12_D13_P

SH4

D12_D13_M

SH4

PARALLELINTERFACE

SERIALINTERFACE

Default:Shunt2-3

Default:Shunt1-2

Default:Shunt2-3

Default:Shunt2-3

R17

100

R17

100

1

2

R11

1K

R11

1K

12

R10

10K

R10

10K

12

TP5TP5

R6

10K

R6

10K

12

R20

100

R20

100

1

2

SW1SW1

C13

.1uF

C13

.1uF

12

J4J4

2

4

6

8

1

3

5

7

R14

1K

R14

1K

12

R8

100

R8

100

1

2

J2J2

1

2

3

U1

ADS614X

U1

ADS614X

DRVDD

1

RESET

2

SCLK

3

SDATA

4

SEN

5

AGND

6

CLKP

7

CLKM

8

AGND

9

INP

10

INM

11

AGND

12

AVDD

13

CM_REFIN

14

AVDD_FVDD

15

PDN

16

D0_D1_M

17

D0_D1_P

18

D2_D3_M

19

D2_D3_P

20

D4_D5_M

21

D4_D5_P

22

D6_D7_M

23

D6_D7_P

24

CLKOUTM

25

CLKOUTP

26

D8_D9_M

27

D8_D9_P

28

D10_D11_M

29

D10_D11_P

30

D12_D13_M

31

D12_D13_P

32

DRVSS(GNDPAD)

33

R64

0OHM

DoNotInstall

R64

0OHM

DoNotInstall

J7J7

1

2

3

TP6TP6

R7

0OHM

R7

0OHM

R9

1K

R9

1K

12

R18

10K

R18

10K

12

C12

.1uF

C12

.1uF

12

TP1TP1

R19

100

R19

100

1

2

R13

100

R13

100

1 2

TP3TP3

TP2TP2

R15

10K

R15

10K

12

C85

.1uF

C85

.1uF

12

R62

0OHM

DoNotInstall

R62

0OHM

DoNotInstall

J1J1

2

4

6

8

1

3

5

7

J3J3

1

2

3

TP4TP4

C11

.1uF

C11

.1uF

12

J6J6

1

2

3

R3

1K

R3

1K

12

R12

100

R12

100

1

2

R5

1K

R5

1K

12

J5J5

1

2

3

R63

0OHM

DoNotInstall

R63

0OHM

DoNotInstall

R4

1K

R4

1K

12

R16

10

R16

10

PhysicalDescription

www.ti.com

Figure8.EVMSchematic,Sheet2

24SLAU206B–September2007–RevisedApril2008

SubmitDocumentationFeedback