http://www.tyan.com

52

Chapter 4

BIOS Configuration

PCI1 to PCI0 Access

Set this option to Enabled to enable access between two different PCI buses

(PCI1 and PCI0). The settings are Enabled or Disabled.

Method of Memory Detection

This option determines how your system will detect the type of system

memory you have installed. Options are Auto+SPD or Auto only.

DRAM Integrity Mode

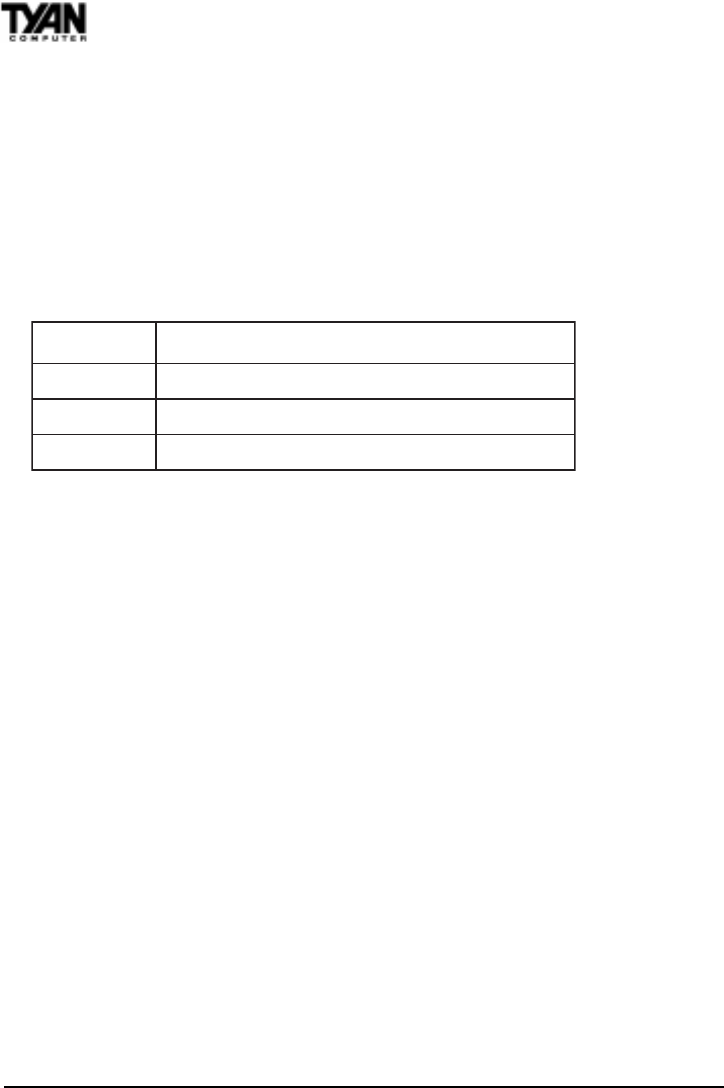

This option sets the type of system memory checking. The settings are:

DRAM Refresh Rate

This option specifies the interval between refresh signals to DRAM system

memory. The settings are 15.6 us (microseconds), 31.2 us, 62.4 us, 124.8 us, or

249.6 us.

Memory Hole

This option specifies the location of an area of memory that cannot be

addressed on the ISA bus. The settings are Disabled, 512KB-640KB, or 15MB-

16MB.

SDRAM RAS# to CAS# Delay

This option specifies the length of the a inserted between the RAS and CAS

signals of the DRAM system memory access cycle if SDRAM is installed. The

settings are Auto, 2 SCLKs or 3 SCLKs. The Optimal default setting is Auto.

SDRAM RAS# Precharge

(CHANGE) This option specifies the length of the RAS precharge part of the

DRAM system memory access cycle when SDRAM system memory is

installed in this computer. The settings are Auto, 2 SCLKs, or 3 SCLKs.

Power Down SDRAM

If this option is set to Enabled, the SDRAM Power Down feature is enabled.

The settings are Enabled or Disabled.

gnitteSnoitpircseD

CCEnoN .enodsignitroperrorrerognikcehcrorreoN

CE .edameblliwsnoitcerrocontub,detcetederasrorrE

erawdraHCCE .detcerrocerasrorretibelgnisdna,detcetederasrorrE