ChipScope PLBv46 IBA (Bus Analyzer) (v1.00a)

DS619 (v1.0) September 17, 2007 www.xilinx.com

Product Specification 3

R

P34 MU_2C PLB_TAttribute[0:15] Slave I PLB Transfer Attribute

Address

P35 MU_3A PLB_ABus[0:31] Slave I PLB address bus, lower 32 bits

P36 MU_3B PLB_UABus[0:31] Slave I PLB address bus, upper 32 bits

Data

P37 MU_4 PLB_wrDBus[0: C_PLBV46_DWIDTH-1] Slave I PLB write data bus

P38 MU_5 PLB_SrdDBus[0:

C_PLBV46_DWIDTH-1]

Sim I Output of SL_rdDBus OR gate

Slave

P39 MU_6A PLB_rdPrim[0:

C_PLBV46_NUM_SLAVES-1]

Slave I PLB secondary to primary read request

indicator

P40 MU_6A PLB_wrPrim[0:

C_PLBV46_NUM_SLAVES-1]

Slave I PLB secondary to primary write request

indicator

P41 MU_6A Sl_AddrAck[0:

C_PLBV46_NUM_SLAVES-1]

Slave I Slave Address acknowledge

P42 MU_6A Sl_Rearbitrate[0:

C_PLBV46_NUM_SLAVES-1]

Slave I Slave bus re-arbitrate indicator

P43 MU_6A Sl_wait[0: C_PLBV46_NUM_SLAVES-1] Slave I Slave wait indicator

P44 MU_6A Sl_rdBTerm[0:

C_PLBV46_NUM_SLAVES -1]

Slave I Slave terminate read burst indicator

P45 MU_6A Sl_rdComp[0:

C_PLBV46_NUM_SLAVES -1]

Slave I Slave read transfer complete indicator

P46 MU_6A Sl_rdDAck[0:

C_PLBV46_NUM_SLAVES-1]

Slave I Slave read data acknowledge

P47 MU_6A Sl_wrBTerm[0:

C_PLBV46_NUM_SLAVES -1]

Slave I Slave terminate write burst indicator

P48 MU_6A Sl_wrComp[0:

C_PLBV46_NUM_SLAVES -1]

Slave I Slave write transfer complete indicator

P49 MU_6A Sl_wrDAck[0:

C_PLBV46_NUM_SLAVES-1]

Slave I Slave write data acknowledge

P50 MU_6B Sl_rdWdAddr[0:

C_PLBV46_NUM_SLAVES*4-1]

Slave I Slave read word address

P51 MU_6B Sl_SSize[0:

C_PLBV46_NUM_SLAVES*2-1]

Slave I Slave data bus port size indicator

P52 MU_7 Sl_MBusy[0: C_PLBV46_NUM_SLAVES

*C_PLBV46_NUM_MASTERS-1]

Slave I Slave busy indicator

P53 MU_8 Sl_MRdErr[0:

C_PLBV46_NUM_SLAVES

*C_PLBV46_NUM_MASTERS-1]

Slave I Slave read error indicator

P54 MU_9 Sl_MWrErr[0:

C_PLBV46_NUM_SLAVES

*C_PLBV46_NUM_MASTERS-1]

Slave I Slave write error indicator

PLB Arbitration Signals

P55 MU_10 M_request[0:

C_PLBV46_NUM_MASTERS-1]

Master I Master bus request

P56 MU_10 M_priority[0:

C_PLBV46_NUM_MASTERS*2-1]

Master I Master bus request priority

P57 MU_10 M_busLock[0:

C_PLBV46_NUM_MASTERS-1]

Master I Master Bus Lock

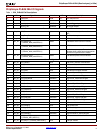

Table 1: IBA_PLBv46 Pin Descriptions (Continued)

Port MU Signal Name Interface I/O Description