3-10 Chapter 3

DRAM Clock (Mhz):

This item sets the DRAM clock of your DRAM module. The system may be unstable or unable to boot up

if your DRAM module does not support the clock you set.

DRAM Command Rate:

When the host (northbridge) locates the desired memory address, it then processes the wait state of

commands.

DRAM CAS# latency Time:

You can select SDRAM CAS (Column Address Strobe) latency time according your SDRAM

specification.

# LDT & PCI Bus Control:

Click <Enter> key to enter its submenu:

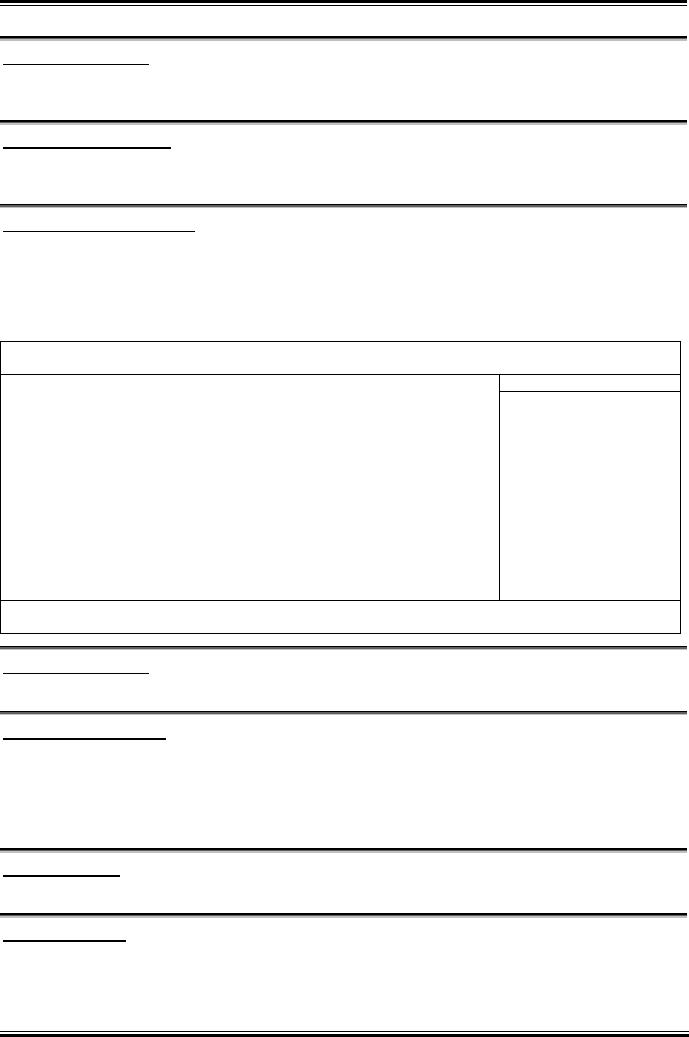

Phoenix – Award WorkstationBIOS CMOS Setup Utility

LDT & PCI Control

LDT Bus Frequency 800mhz Item Help

PCI Delay Transaction

↑↓:Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5: Previous Values F6: Fail-Safe Defaults F7: Optimized Defaults

LDT Bus Frequency:

This item allows you to select LDT Bus Frequency.

PCI Delay Transaction:

Two options are available: Disabled or Enabled. The default setting is Enabled. The chipset has an

embedded 32-bit posted write buffer to support delay transactions cycles. Select Enabled to support

compliance with PCI specification version 2.2.

# Back to Advanced Chipset Features Setup Menu:

Vlink Data Rate:

This item can let you select the Vlink Data Rate between northbridge and southbridge.

Init Display First:

This item selects to initialize AGP or PCI Slot first when the system boots.

[PCI Slot]: When the system boots, it will first initialize PCI.

[AGP]: When the system boots, it will first initialize AGP.

KV-85