22 333 FSB AMD Sempron™ Processor Model 10 with 256K L2 Cache Specifications Chapter 6

AMD Sempron™ Processor Model 10 with 256K L2 Cache Data Sheet 31994A —1 August 2004

6.2 333 FSB AMD Sempron™ Processor Model 10 SYSCLK and

SYSCLK# AC Characteristics

Table 2 shows the SYSCLK/SYSCLK# differential clock AC

characteristics of this processor.

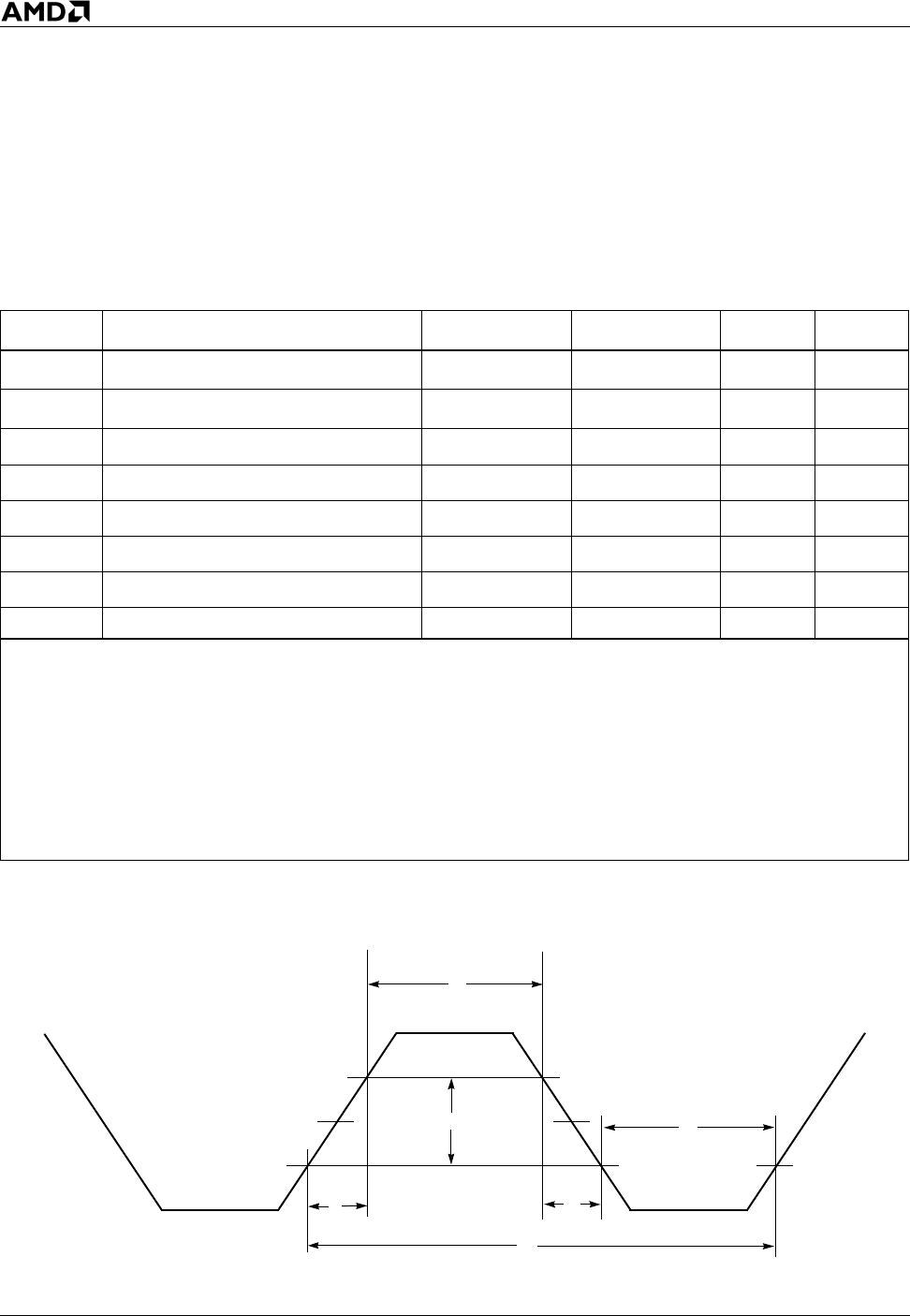

Figure 8 shows a sample waveform of the SYSCLK signal.

Figure 8. SYSCLK Waveform

Table 2. 333 FSB SYSCLK and SYSCLK# AC Characteristics

Symbol Parameter Description Minimum Maximum Units Notes

Clock Frequency 50 166 MHz 1

Duty Cycle 30% 70%

t

1

Period 6 ns 2, 3

t

2

High Time 1.0 ns

t

3

Low Time 1.0 ns

t

4

Fall Time 2 ns

t

5

Rise Time 2 ns

Period Stability ± 300 ps

Notes:

1. The AMD Athlon™ system bus operates at twice this clock frequency.

2. Circuitry driving the AMD Athlon system bus clock inputs must exhibit a suitably low closed-loop jitter bandwidth to allow the PLL

to track the jitter. The –20dB attenuation point, as measured into a 20

- or 30-pF load must be less than 500 kHz.

3. Circuitry driving the AMD Athlon system bus clock inputs may purposely alter the AMD Athlon system bus clock frequency (spread

spectrum clock generators). In no cases can the AMD

Athlon system bus period violate the minimum specification above.

AMD

Athlon system bus clock inputs can vary from 100% of the specified frequency to 99% of the specified frequency at a

maximum rate of 100 kHz.

t

5

V

CROSS

t

2

t

3

t

4

t

1

V

Threshold-AC