AMD Geode™ GX Processor/CS5535 Companion Device GeodeROM Porting Guide 15

4

Initialization 32430C

4.0Initialization

4.1 Processor Initialization

The AMD Geode™ GX processor contains many of the components normally found in system support chipsets.

GeodeROM must set up these components, including the DRAM controller, L1 cache controller, clock control, and PCI con-

troller as well as some proprietary systems like GeodeLink™ architecture.

This chapter contains descriptions and some pseudo code for GX processor-specific code sequences in GeodeROM. The

modifications are grouped into CPU core initialization, DRAM controller initialization, GeodeLink interface initialization, PCI

bus initialization, and miscellaneous other initializations/changes.

4.1.1 Set Clocks and Reset

Register: GLCP_SYS_RSTPLL (GX GLCP MSR Address 4C000014h)

The GX processor has separate clocks for the CPU core and GeodeLink interface. These clocks are derived from the sys-

tem PLL, which is driven by the PCI clock. At power-on, these clocks default to a safe value. Setting the clock registers and

doing a reset will re-clock the GX processor.

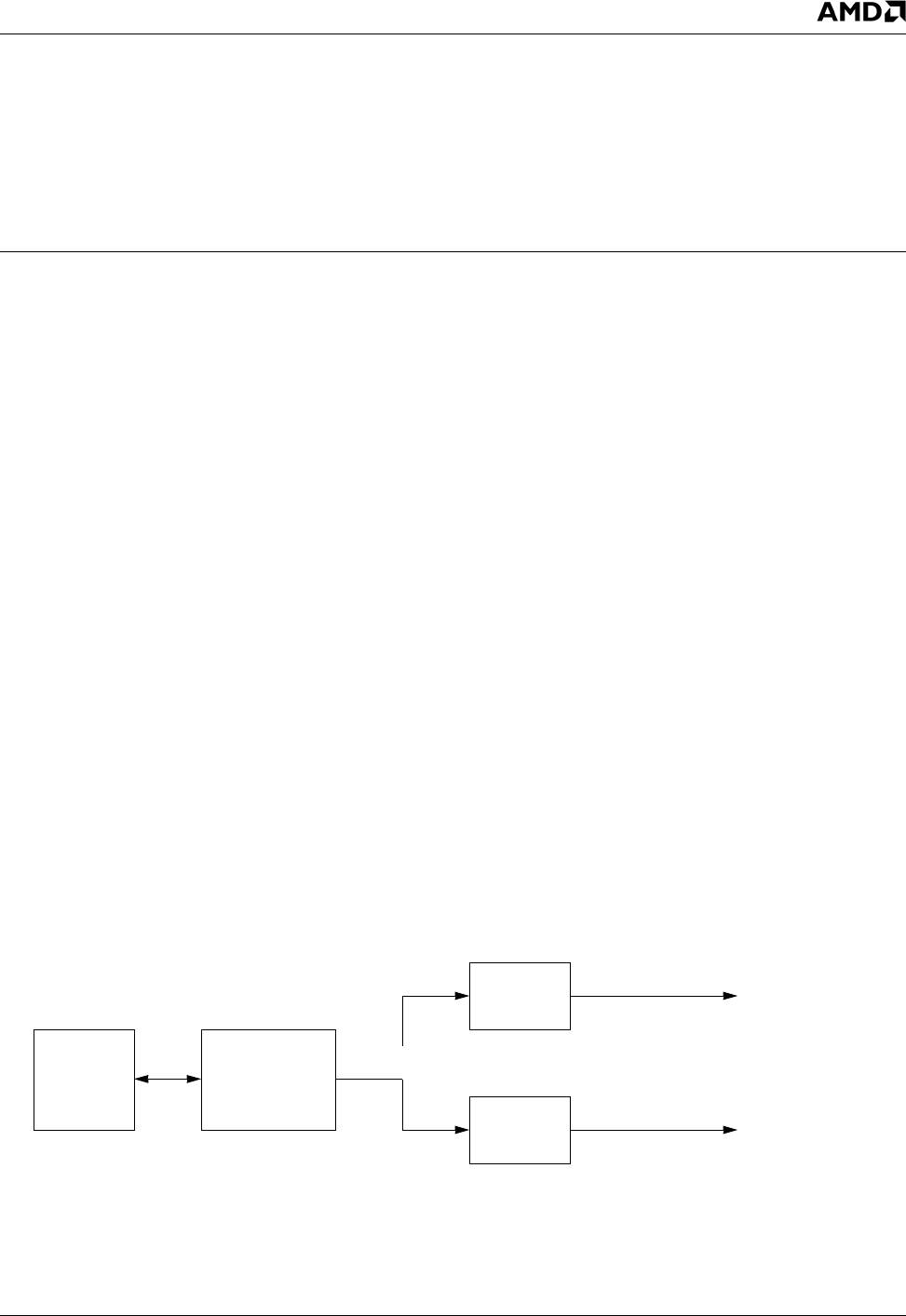

The clocks are controlled by three divisors as shown in Figure 4-1. The Feed-back Divisor (FbDIV) in the PLL sets

sppl_raw_clk. Sppl_raw_clk is divided by the GeodeLink Divisor (MDIV) and the CPU Divisor (VDIV) to derive GeodeLink

clock and CPU clock. Sppl_raw_clk must be between 300 MHz and 800 MHz. The GeodeLink clock is used to clock the

memory. Therefore, the GeodeLink clock should never be greater than the speed and type of the system memory.

All the divisor bits, software bits, memory type bit, and reset bits are located in the GLCP_SYS_RSTPLL register. Once the

divisors and memory type (DDR/SDR) are set, the BIOS sets a reset flag and resets the CPU to continue initialization at the

desired CPU speed.

GeodeROM sets the clocks based on jumper settings that are interpreted to match SKUs defined for that version of the

CPU. SKUs are defined by PCI speed, memory type (SDR or DDR), and the jumper setting. GeodeROM can also use

FbDIV, MDIV, and VDIV values set by the user in CMOS for debugging.

If there is an incorrect setting in CMOS setup and the system cannot boot three times in a row, GeodeROM resets CMOS

to the defaults.

See Figure 7-4 on page 33 for example reset and system clock logic.

Figure 4-1. Clock Control

SYSREF

0 - 66 MHz

(PCI Clock)

Clock

System PLL

300 - 800 MHz

Clock

FbDIV

spll_raw-clk

MDIV

VDIV

GLIU Clock

CPU Core Clock