AMD Geode™ GX Processor/CS5535 Companion Device GeodeROM Porting Guide 19

Initialization

32430C

Registers:

CR0

RCONF MSRs: CPU Core MSR Address 00001808h-00001817h

Instruction Memory Configuration Register: CPU Core MSR Address 00001700h

Data Memory Configuration Register: CPU Core MSR Address 00001800h

Entry Conditions:

None

Procedure:

IF <L1 cache requested>

Setup the Default Region Configuration Properties and any other RCONFs required.

Write Cache Disable and Not Write-Through bits (bits [30:29]) in the CR0 register.

WBINVD

ENDIF

Note: See Figure 7-2 on page 31 for a pictorial presentation.

GLPCI Regions

The GLPCI has similar MSRs to the CPU Core Region Configuration registers for inbound transactions. These memory

regions control the memory hole from 6460 KB to 1 MB. Six flexible region MRSs are assigned: Memory Region 0 Configu-

ration (R0) through Memory Region 5 Configuration (R5).

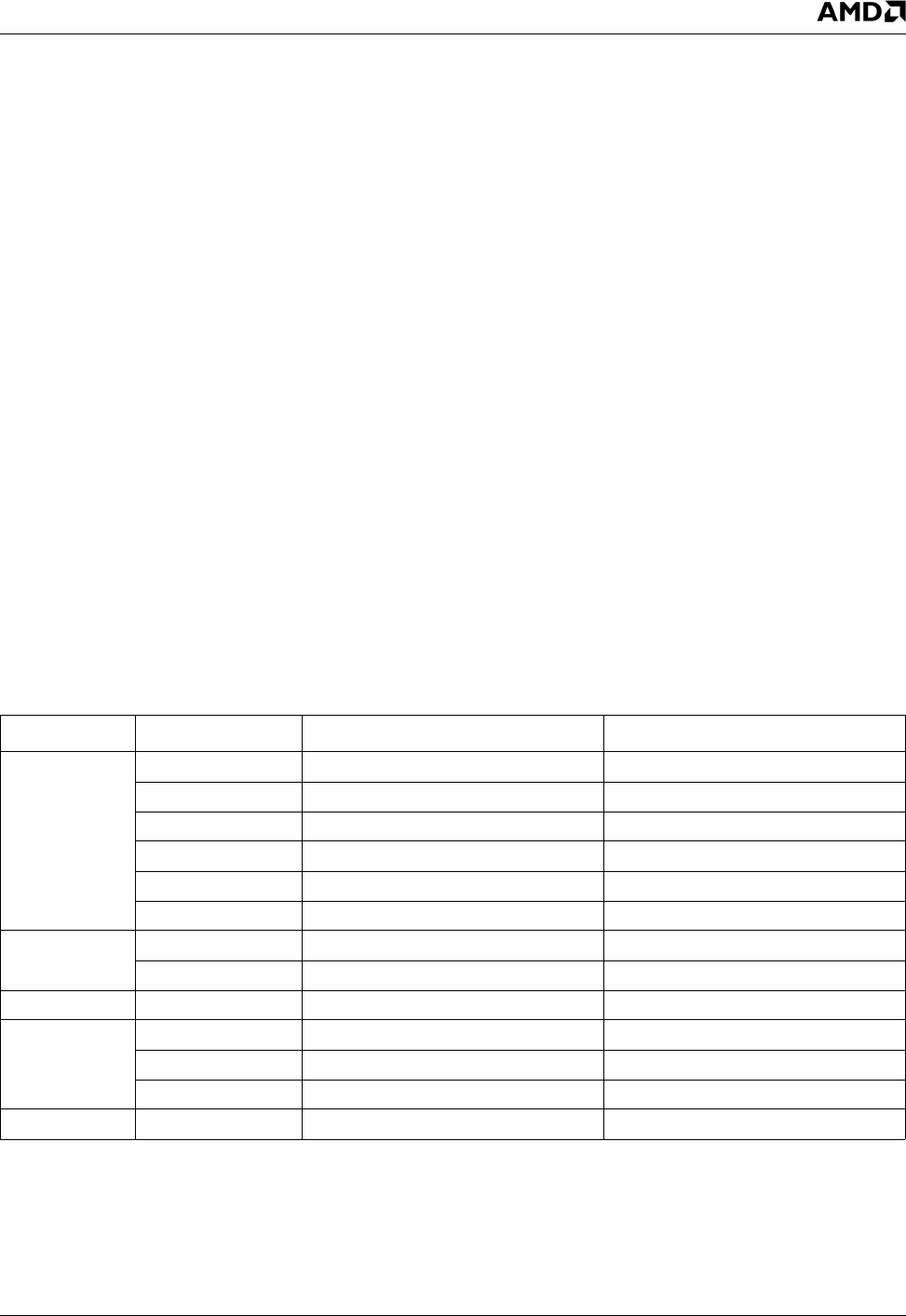

Descriptor Allocation

Register: PHY_CAP (MSR Address GLIU0: 10000086h, GLIU1: 40000086h)

Each GLIU descriptor allocation is defined in the PHY_CAP register.

Descriptor MSR Address GLIU0 GLIU1

P2D_BM 10000020h 00000000h-00007FFFh 00000000h-00007FFFh

10000021h 00080000h-0009FFFFh 00080000h-0009FFFFh

10000022h 4FFFC000h-4FFFFFFFh 4FFFC000h-4FFFFFFFh

10000023h 000A0000h-000BFFFFh 000A0000h-000BFFFFh

10000024h Not used by GeodeROM. Not used by GeodeROM.

10000025h Not used by GeodeROM. Not used by GeodeROM.

P2D_BMO 10000026h 40400000h-4043FFFFh 40400000h-4043FFFFh

10000027h Not used by GeodeROM. Not used by GeodeROM.

P2D_R 10000028h 00100000h-0E7BFFFFh 00100000h-0E7BFFFFh

P2D_RO 10000029h 50000000h-517FFFFFh 50000000h-517FFFFFh

1000002Ah 4FFF8000h-4FFFBFFFh 4FFF8000h-4FFFBFFFh

1000002Bh Not used by GeodeROM. Not used by GeodeROM.

P2D_SC 1000002Ch C000C7FFh, E000FFFFh C000C7FFh, E000FFFFh