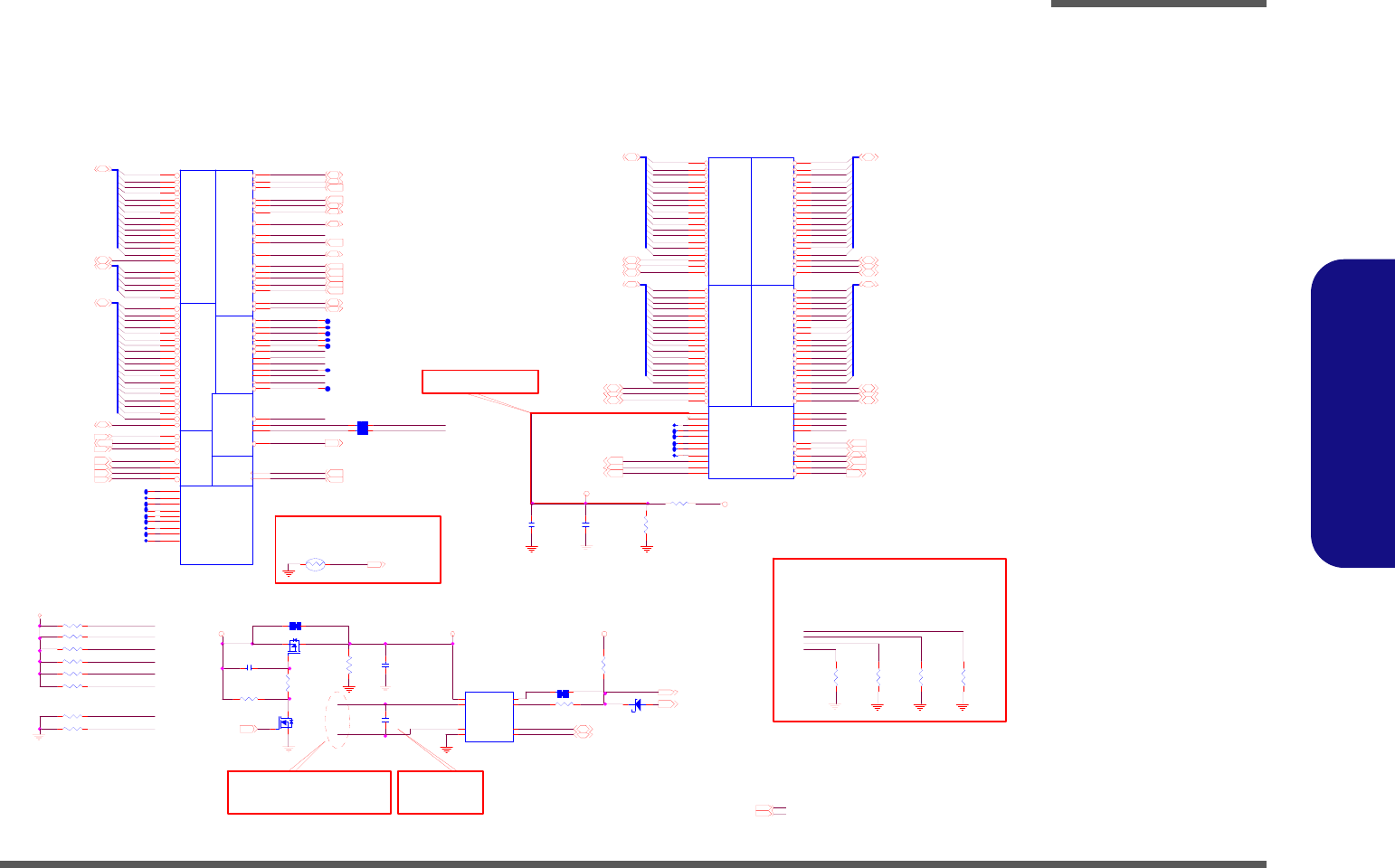

Schematic Diagrams

Intel Penryn (Socket-P) 1/2 B - 3

B.Schematic Diagrams

Intel Penryn (Socket-P) 1/2

Sheet 2 of 40

Intel Penryn

(Socket-P) 1/2

H_BNR # [4]

R5 1K_1%_04

H_A#4

H_D#63

V_THRM

TR1

*TSM1A103H34D3R

CLK_CPU_BC LK# [18]

H _DSTBN#0[4]

H_NMI[13]

CPU_BSEL1[4,18]

H_D#27

H_DEFER # [4]

H_A#26

R4

2K_1%_04

H_DSTBN#2 [4]

THERM_RST#[26]

H_D#25

H_A#9

H_A#18

H_A#[35:3][4]

H_DBSY # [4]

H_HITM# [4]

H_A#7

H_A#34

H_PREQ#

H_D#28

C337

*0.01U_16V_X7R_04

1.05VS

C336

1U_6.3V_04

H_THERM DA

H_D#21

H_D#6

H_D#1

H_D#41

H_D#44

H_RS#2 [4]

H_D#59

H_D#19

H_A#10

COMP2

H_D#23

R8

54.9_1%_04

R200

*1 0 0K_ 04

H_D#26

PM_THRM# [15]

COMP2

H_D#33

SMC_CPU_THE RM [26]

H_D#31

H_D#29

C7

*1U_6.3V_X5R_06

? ADT7421 Colay

PSI# [31]

H_D#57

R211

*330K_04

H_RS#1 [4]

H_A#25

H_REQ#2

R7 54.9_1%_04

H_DIN V#1[4]

R197 56_04

H_ADS# [4]

H_DINV#3 [4]

H_A#12

H_D#30

H_REQ#4

H_D#53

H_A#14

R173 54.9_1%_04

R209

*100K_04

ADDR

GROUP_0

ADDR

GROUP_1

CONTROL

XD P /ITP S I GNALS

H C LK

TH ERMA L

RESERVED

ICH

U9A

MOLEX_47430-6215

N3

P5

P2

L2

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

J4

U2

V4

M4

N5

T2

V3

B2

D2

D22

L5

L4

K5

M3

N2

J1

A6

H1

M1

V1

D3

A22

A21

E2

AD4

AD3

AD1

AC4

G5

F1

C20

E1

H5

F21

A5

G6

E4

D20

C4

B3

C6

B4

H4

AC2

AC1

D21

K3

H2

K2

J3

L1

C1

F3

F4

G3

A3

D5

AC5

AA6

AB3

C7

A24

B25

AB5

G2

AB6

W3

AA4

AB2

AA3

F6

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[3]#

A[30]#

A[31]#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A20M#

ADS#

ADSTB[0]#

ADSTB[1]#

RSVD[08]

BCLK[0]

BCLK[1]

BNR#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

BPRI#

BR0#

DBR#

DBSY#

DEFER#

DRD Y#

FERR#

HI T#

HITM#

IER R#

IG NNE #

INI T#

LINT0

LINT1

LO C K#

PRDY#

PREQ#

PROCHOT#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

RESE T#

RS[0]#

RS[1]#

RS[2]#

SMI#

STPCLK#

TC K

TDI

TDO

THERMTRIP#

TH ERMD A

THERMDC

TM S

TRDY#

TRST#

A[32]#

A[33]#

A[34]#

A[35]#

RSVD[09]

H_A#31

H_RS#0 [4]

H_D#34

R195 *10mil_short

V_THRM

SMD_CPU_THE RM [26]

PM_THRM TRIP# [5,13,28]

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms

COMP1, COMP3: 0.5" Max, Zo=55 Ohms

Best estimate is 18 mils wide trace for outer

layers and 14 mils wide trace if on internal

layers.

Put it at central of

CPU socket

H_HIT# [4]

H_DPRSTP# [5,13,31]

CPU ONLY SUPPORT TO 35W

CLK_CPU_BC LK [18]

H_DSTBN#1[4]

H_D#50

H_A#5

H_D#47

H_D#42

R193 *0_04

3.3V

3.3V[12..17,19,20,23,29,30]

H_REQ#3

COMP3

H_INIT# [13]

H_D#[63:0][4]

H_D#38

H_A#13

H_D#22

R171 649_1%_06

Q18 *AO3409

G

DS

Layout Note:

H_PREQ#

H_D#10

U13

aSC 7525

1

2

3

4

5

6

7

8

VDD

D+

D-

THERM

GND

ALERT

SDATA

SCLK

H_A#16

H_A#28

H_D#4

H_D#11

H_D#55

H_TRDY # [4]

H_DSTBP#1[4]

H_D#52

H_PROCHOT#

H_D#51

R6

27.4_1%_04

1.05VS[3..5,7,8,13,16,29]

CPU_BSEL0

C335

1000P_50V_X7R_04

H_D#17

H_THERMDC

H_BPRI# [4]

H_TDI

H_D#61

10mils

H_TMS

CPU_BSEL1

H_CPURST#

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil spacing.

1.05VS

H_A#6

H_A#17

H_A#32

H_TCK

COMP0

H_A#29

H_IERR#

THER M_ALERT# [26]

H_AD STB#1[4]

R210 *10mil_short

H_D#45

R182

54.9_1%_04

12mils

H_INTR[13]

Layout Note:

H_D#3

H_A#11

H_D#12

COMP1

H_CPU RST# [4]

COMP0

H_D#46

H_D#16

H_TDI

H_D#20

H_PR OCH OT#

H_D#48

H_D#24

0.5" max, Zo= 55 Ohms

H_A#23

H_D#54

Near to Thermal

IC

H_D#62

H_DPSLP# [13]

R183

27.4_1%_04

COMP3

H_D#58

H_D#32

H_THER MDC _R

H_DINV#2 [4]

H_DSTBP#3 [4]

R196 *10mil_short

H_STPCLK#[13]

COMP1

CPU_BSEL2

H_REQ#1

H_A#21

H_A#30

H_TRST#

R194

10K_04

H_D#60

H_D#56

D15

ASD751V

AC

CPU TEM P [26]

H_D#8

H_IGNNE#[13]

H_A#15

H_D#18

H_DSTBP#2 [4]

H_A#8

H_TRST#

H_D#2

H_REQ #[4:0][4]

H_IERR#

H_D#5

H_D#39

R19 *51_1%_04

H_DR DY# [4]

H_A#24

H_D#49

H_A#[35:3][4]

H_REQ#0

H_D#15

R198 54.9_1%_04

Q19

*2N7002W

G

DS

Layout note:

H_THERM DC

H_A#19

H_D#7

H_A#22

Layout Note:

H_A20M#[13]

DATA GRP 0 DATA GRP 1

DATA GRP 2DATA GRP 3

MIS C

U9B

MOLEX_47430-6215

R26

U26

AA1

Y1

E22

F24

J24

J23

H22

F26

K22

H23

N22

K25

P26

R23

E26

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

G22

T25

N25

Y22

AB24

V24

V26

V23

T22

U25

U23

F23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

AE24

AD24

G25

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

E25

AC22

AD23

AF22

AC23

E23

K24

G24

AF 1

H25

N24

U22

AC20

E5

B5

D24

J26

L26

Y26

AE25

H26

M26

AA26

AF24

AD26

AE6

D6

D7

C24

B22

B23

C21

D25

AF26

A26

C23

C3

CO MP[0]

CO MP[1]

CO MP[2]

CO MP[3]

D[0]#

D[1]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

D[16]#

D[17]#

D[18]#

D[19]#

D[2]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[3]#

D[30]#

D[31]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[4]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

D[48]#

D[49]#

D[5]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[6]#

D[60]#

D[61]#

D[62]#

D[63]#

D[7]#

D[8]#

D[9]#

TEST5

D INV[0]#

D INV[1]#

DINV[2]#

DINV[3]#

DPRSTP#

DPSLP#

DPWR#

DSTBN[0]#

DSTBN[1]#

DSTBN[2]#

DSTBN[3]#

DSTBP[0]#

DSTBP[1]#

DSTBP[2]#

DSTBP[3]#

GTLREF

PSI#

PWRGOOD

SLP#

TEST3

BSE L[0]

BSE L[1]

BSE L[2]

TEST2

TEST4

TEST6

TEST1

TEST7

H_D#[63:0][4]

H_THERMDA

R192 *10mil_short

H_D#[63:0] [4]

H_PWRGD [13]

H_AD STB#0[4]

H_LOCK# [4]

Layout Note:

H_A#33

H_A#27

H_TMS

CPU_BSEL2[4,18]

H_A#35

H_D#36

H_BREQ# [4]

H_DSTBN#3 [4]

H_A#3

R181 54.9_1%_04

H_CPUSLP# [4]

H_D#40

CPU_GTLREF

H_FERR #[13]

H_DINV#0[4]

H_D#9

H_D#43

R174 54.9_1%_04

H_DSTBP#0[4]

H_D#14

H_SMI#[13]

H_D#[63:0] [4]

H_D#0

CPU_BSEL0[4,18]

H_DPWR# [4]

H_D#35

H_D#37

H_D#13

CPU_GRFE=0.7V

H_A#20

H_TCK

H_THERMDA_R

H_CPURST#

C8

0.01U_16V_X7R_04