CY14B101L

Document Number: 001-06400 Rev. *I Page 12 of 18

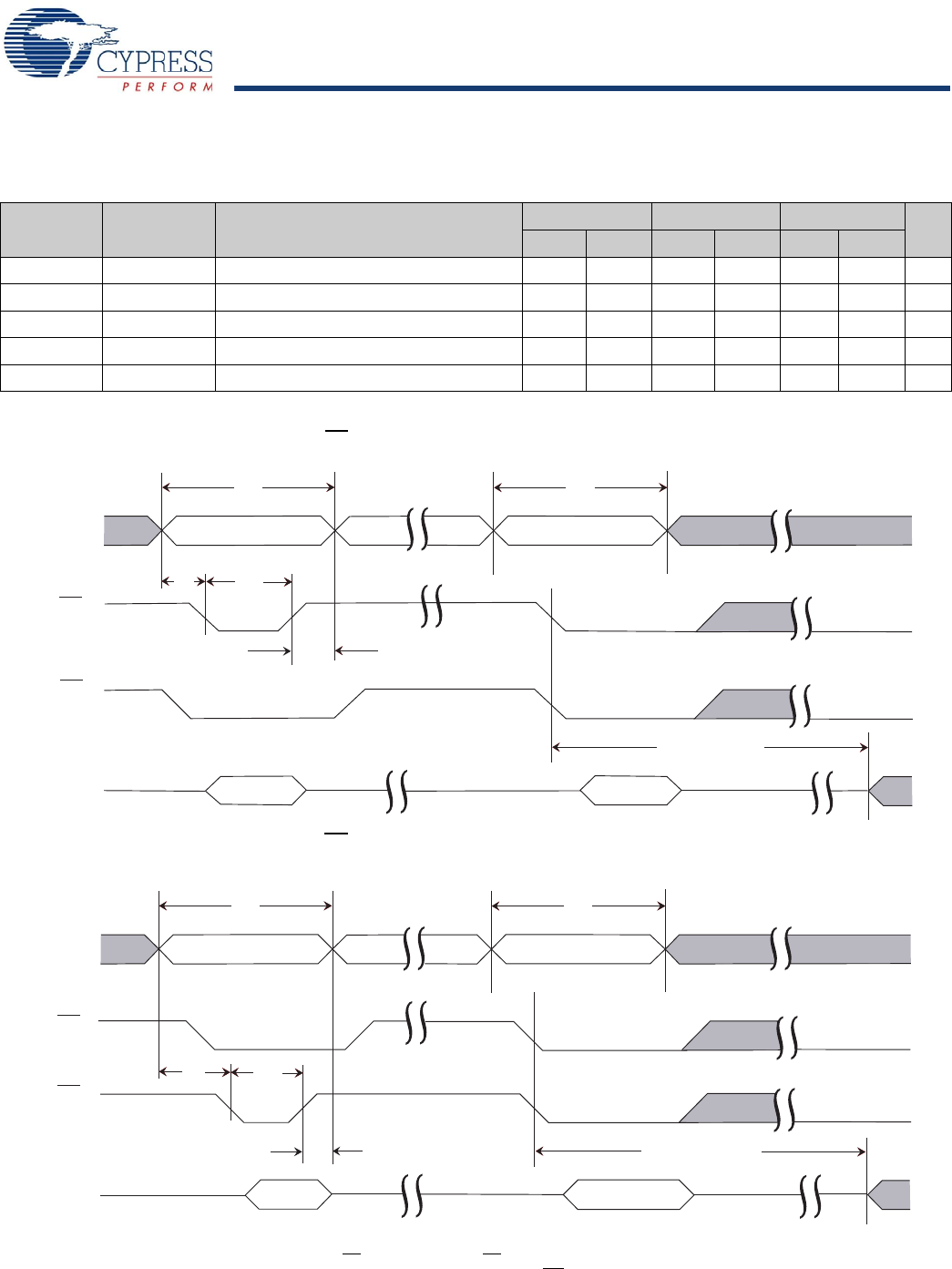

Software Controlled STORE/RECALL Cycle

The software controlled STORE/RECALL cycle follows.

[16, 17]

Parameter Alt Description

25 ns 35 ns 45 ns

Unit

Min Max Min Max Min Max

t

RC

[17]

t

AVAV

STORE/RECALL Initiation Cycle Time 25 35 45 ns

t

SA

t

AVEL

Address Setup Time 0 0 0 ns

t

CW

t

ELEH

Clock Pulse Width 20 25 30 ns

t

HA

t

GHAX,

t

ELAX

Address Hold Time 1 1 1 ns

t

RECALL

RECALL Duration 120 120 120

μ

s

Switching Waveforms

Figure 10. CE Controlled Software STORE/RECALL Cycle

[17]

Figure 11. OE Controlled Software STORE/RECALL Cycle

[17]

t

RC

t

RC

t

SA

t

SCE

t

HA

t

STORE

/ t

RECALL

DATAVALID

DATAVALID

6#SSERDDA1#SSERDDA

HIGH IMPEDANCE

ADDRESS

CE

OE

DQ (DATA)

t

RC

t

RC

6#SSERDDA1#SSERDDA

ADDRESS

t

SA

t

SCE

t

HA

t

STORE

/ t

RECALL

DATAVALID

DATAVALID

HIGH IMPEDANCE

CE

OE

DQ (DATA)

Notes

16.The software sequence is clocked on the falling edge of CE

controlled READs or OE controlled READs.

17.The six consecutive addresses must be read in the order listed in the Mode Selection table. WE

must be HIGH during all six consecutive cycles.

[+] Feedback