CY14B101L

Document Number: 001-06400 Rev. *I Page 13 of 18

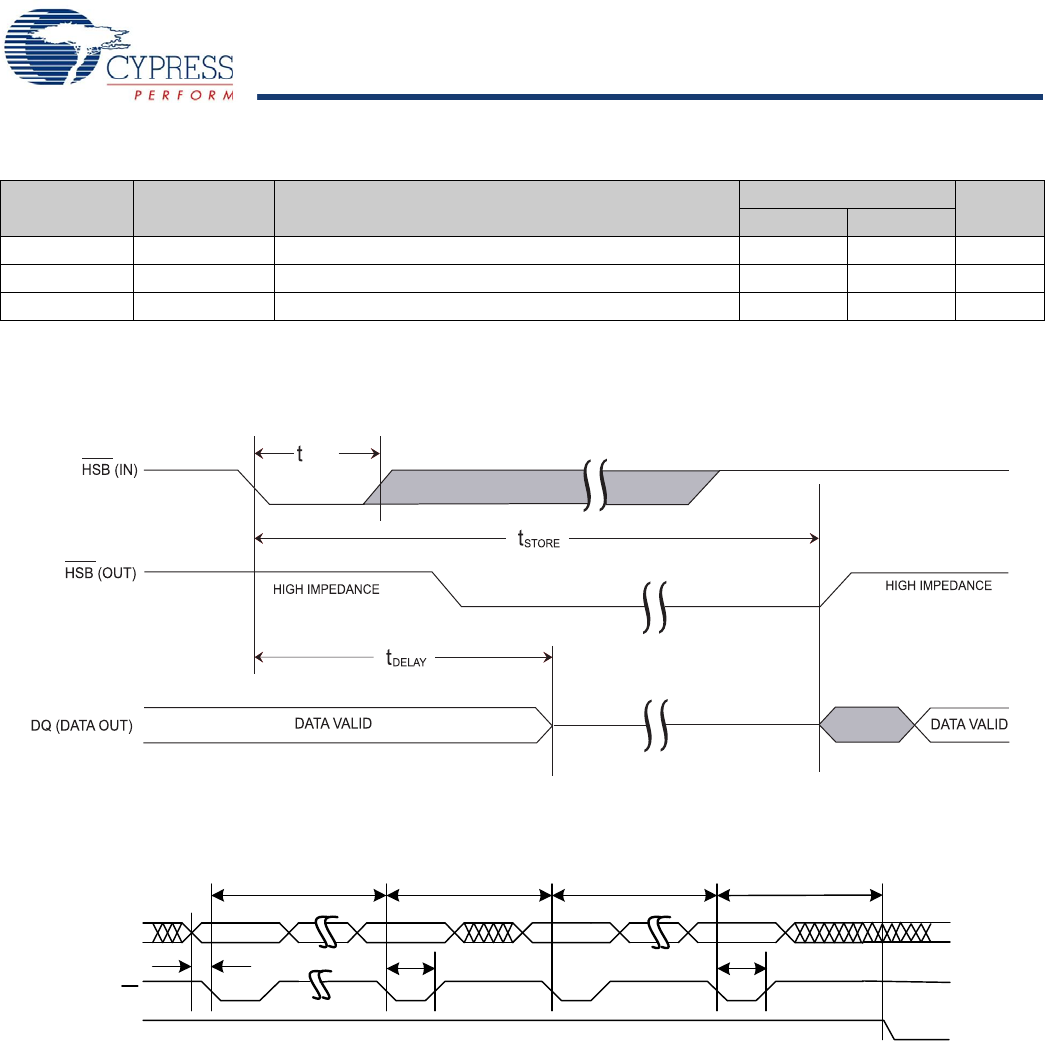

Hardware STORE Cycle

Parameter Alt Description

CY14B101L

Unit

Min Max

t

PHSB

t

HLHX

Hardware STORE Pulse Width 15 ns

t

DELAY

[18]

t

HLQZ ,

t

BLQZ

Time Allowed to Complete SRAM Cycle 1 70

μ

s

t

ss

[19, 20]

Soft Sequence Processing Time 70 us

Switching Waveforms

Figure 12. Hardware STORE Cycle

Figure 13. Soft Sequence Processing

[19, 20]

3+6%

$GGUHVV $GGUHVV $GGUHVV $GGUHVV

6RIW6HTXHQFH

&RPPDQG

W

66

W

66

&(

$GGUHVV

9

&&

W

6$

W

&:

6RIW6HTXHQFH

&RPPDQG

W

&:

Notes

18.On a hardware STORE initiation, SRAM operation continues to be enabled for time t

DELAY

to allow read and write cycles to complete.

19.This is the amount of time to take action on a soft sequence command. Vcc power must remain high to effectively register command.

20.Commands such as Store and Recall lock out I/O until operation is complete which further increases this time. See specific command.

[+] Feedback