MoBL

®

CY62128E

Document #: 38-05485 Rev. *F Page 2 of 12

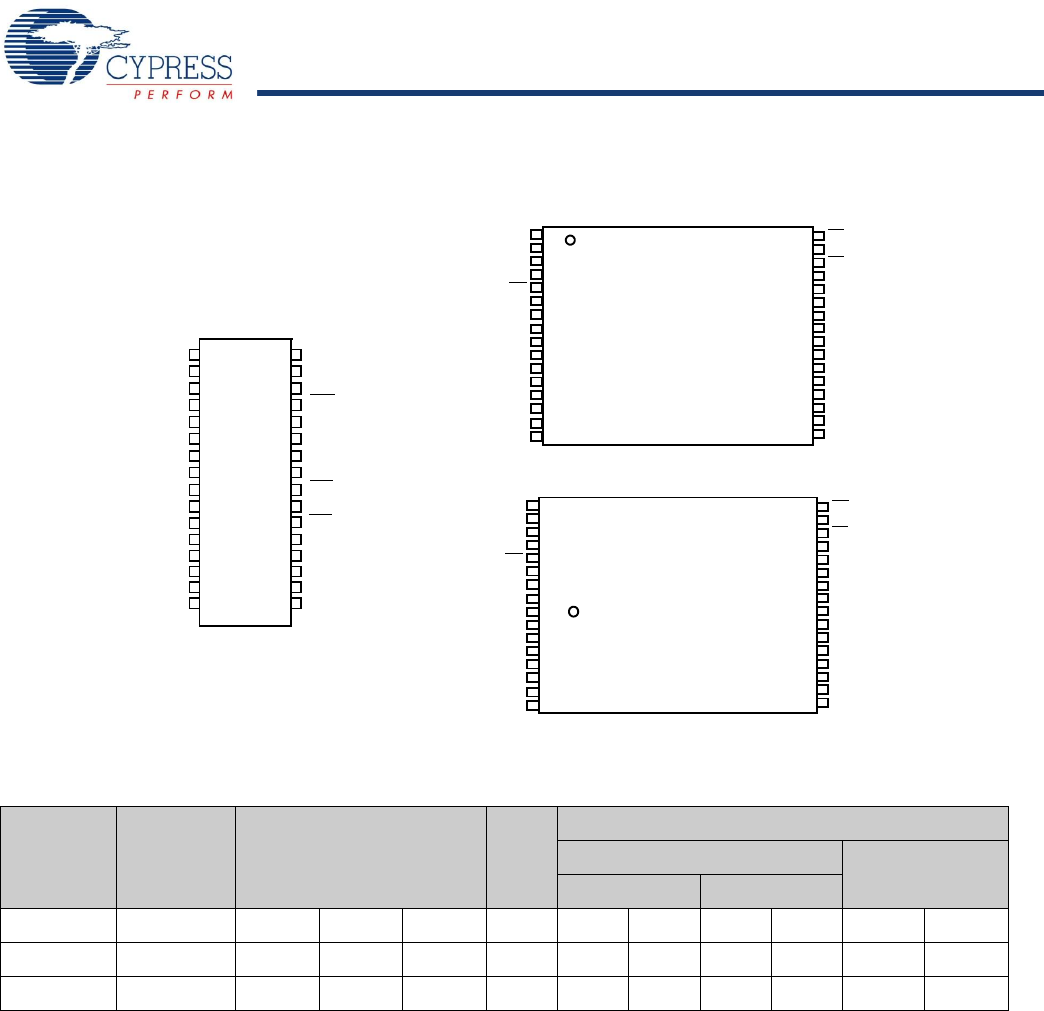

Pin Configuration

[2]

Product Portfolio

Product Range V

CC

Range (V)

Speed

(ns)

Power Dissipation

Operating I

CC

(mA)

Standby I

SB2

(µA)

f = 1MHz f = f

max

Min Typ

[3]

Max Typ

[3]

Max Typ

[3]

Max Typ

[3]

Max

CY62128ELL Ind’l/Auto-A 4.5 5.0 5.5 45

[4]

1.3 2 11 16 1 4

CY62128ELL Auto-E 4.5 5.0 5.5 55 1.3 4 11 35 1 30

A

6

A

7

A

16

A

14

A

12

WE

V

CC

A

4

A

13

A

8

A

9

OE

STSOP

Top View

(not to scale)

30

28

29

31

24

19

23

22

21

20

18

13

17

16

15

14

11

12

IO

2

IO

1

GND

IO

7

IO

4

IO

5

IO

6

IO

0

CE

1

A

11

A

5

9

10

32

1

2

3

4

5

6

7

8

CE

2

A

15

NC

A

10

IO

3

A

1

A

0

A

3

A

2

26

25

26

27

A

6

A

7

A

16

A

14

A

12

WE

V

CC

A

4

A

13

A

8

A

9

OE

TSOP I

Top View

(not to scale)

1

6

2

3

4

5

7

32

27

31

30

29

28

26

21

25

24

23

22

19

20

IO

2

IO

1

GND

IO

7

IO

4

IO

5

IO

6

IO

0

CE

1

A

11

A

5

17

18

8

9

10

11

12

13

14

15

16

CE

2

A

15

NC

A

10

IO

3

A

1

A

0

A

3

A

2

1

2

3

4

5

6

7

8

9

10

11

14

31

32

12

13

16

15

29

30

21

22

19

20

27

28

25

26

17

18

23

24

32-Pin SOIC

Top View

NC

A

16

A

15

A

14

A

13

A

12

A

11

A

10

A

9

A

8

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

IO

0

IO

1

IO

2

IO

3

IO

4

IO

5

IO

6

IO

7

V

SS

V

CC

CE

2

WE

OE

CE

1

Notes

2. NC pins are not connected on the die.

3. Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at V

CC

= V

CC(typ)

, T

A

= 25°C.

4. When used with a 100 pF capacitive load and resistive loads as shown on page 4, access times of 55 ns (t

AA

, t

ACE

) and 25 ns (t

DOE

) are guaranteed.

[+] Feedback