CY7B991

CY7B992

Document Number: 38-07138 Rev. *B Page 8 of 19

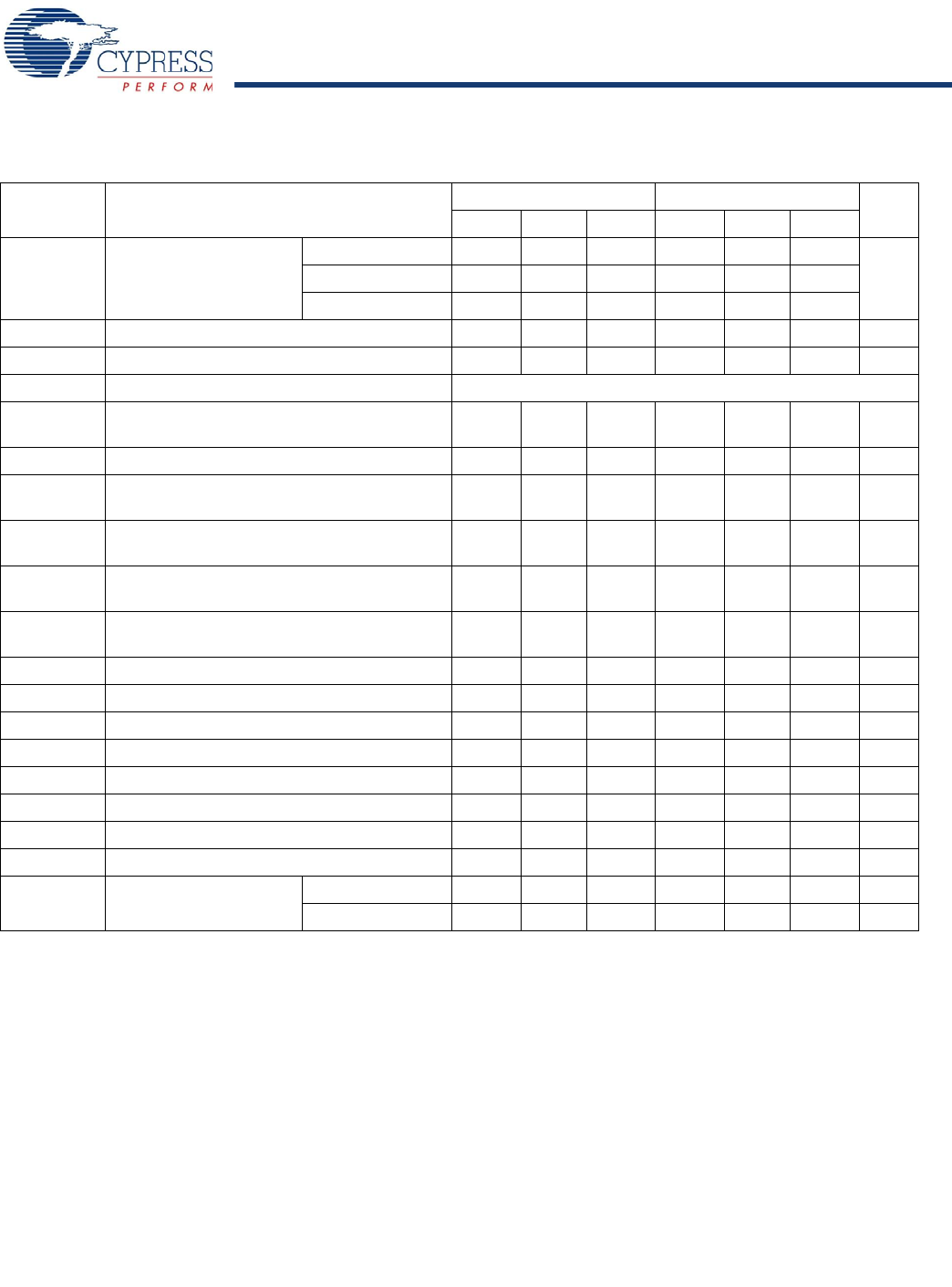

Switching Characteristics Over the Operating Range

[2, 13]

CY7B991–2

[14]

CY7B992–2

[14]

Parameter Description Min Typ Max Min Typ Max Unit

f

NOM

Operating Clock

Frequency in MHz

FS = LOW

[1, 2]

15 30 15 30 MHz

FS = MID

[1, 2]

25 50 25 50

FS = HIGH

[1, 2 , 3]

40 80 40 80

[15]

t

RPWH

REF Pulse Width HIGH 5.0 5.0 ns

t

RPWL

REF Pulse Width LOW 5.0 5.0 ns

t

U

Programmable Skew Unit See Table 1

t

SKEWPR

Zero Output Matched-Pair Skew

(XQ0, XQ1)

[16, 17]

0.05 0.20 0.05 0.20 ns

t

SKEW0

Zero Output Skew (All Outputs)

[16, 18,19]

0.1 0.25 0.1 0.25 ns

t

SKEW1

Output Skew (Rise-Rise, Fall-Fall, Same

Class Outputs)

[16, 19]

0.25 0.5 0.25 0.5 ns

t

SKEW2

Output Skew (Rise-Fall, Nominal-Inverted,

Divided-Divided)

[16, 19]

0.3 0.5 0.3 0.5 ns

t

SKEW3

Output Skew (Rise-Rise, Fall-Fall, Different

Class Outputs)

[16, 19]

0.25 0.5 0.25 0.5 ns

t

SKEW4

Output Skew (Rise-Fall, Nominal-Divided,

Divided-Inverted)

[16, 19]

0.5 0.9 0.5 0.7 ns

t

DEV

Device-to-Device Skew

[14, 21]

0.75 0.75 ns

t

PD

Propagation Delay, REF Rise to FB Rise –0.25 0.0 +0.25 –0.25 0.0 +0.25 ns

t

ODCV

Output Duty Cycle Variation

[22]

–0.65 0.0 +0.65 –0.5 0.0 +0.5 ns

t

PWH

Output HIGH Time Deviation from 50%

[23, 24]

2.0 3.0 ns

t

PWL

Output LOW Time Deviation from 50%

[23, 24]

1.5 3.0 ns

t

ORISE

Output Rise Time

[23, 25]

0.15 1.0 1.2 0.5 2.0 2.5 ns

t

OFALL

Output Fall Time

[23, 25]

0.15 1.0 1.2 0.5 2.0 2.5 ns

t

LOCK

PLL Lock Time

[26]

0.5 0.5 ms

t

JR

Cycle-to-Cycle Output

Jitter

RMS

[14]

25 25 ps

Peak-to-Peak

[14]

200 200 ps

Notes

12.CMOS output buffer current and power dissipation specified at 50 MHz reference frequency.

13.Test measurement levels for the CY7B991 are TTL levels (1.5V to 1.5V). Test measurement levels for the CY7B992 are CMOS levels (VCC/2 to VCC/2). Test

conditions assume signal transition times of 2 ns or less and output loading as shown in the AC Test Loads and Waveforms unless otherwise specified.

14.Guaranteed by statistical correlation. Tested initially and after any design or process changes that affect these parameters.

15.Except as noted, all CY7B992–2 and –5 timing parameters are specified to 80 MHz with a 30 pF load.

16.SKEW is defined as the time between the earliest and the latest output transition among all outputs for which the same tU delay is selected when all are loaded

with 50 pF and terminated with 50Ω to 2.06V (CY7B991) or VCC/2 (CY7B992).

17.tSKEWPR is defined as the skew between a pair of outputs (XQ0 and XQ1) when all eight outputs are selected for 0tU.

18.tSKEW0 is defined as the skew between outputs when they are selected for 0tU. Other outputs are divided or inverted but not shifted.

19.CL=0 pF. For CL=30 pF, tSKEW0=0.35 ns.

20.There are three classes of outputs: Nominal (multiple of tU delay), Inverted (4Q0 and 4Q1 only with 4F0 = 4F1 = HIGH), and Divided (3Qx and 4Qx only in

Divide-by-2 or Divide-by-4 mode).

21.tDEV is the output-to-output skew between any two devices operating under the same conditions (VCC ambient temperature, air flow, and so on.)

22.tODCV is the deviation of the output from a 50% duty cycle. Output pulse width variations are included in tSKEW2 and tSKEW4 specifications.

23.Specified with outputs loaded with 30 pF for the CY7B99X–2 and –5 devices and 50 pF for the CY7B99X–7 devices. Devices are terminated through 50Ω to

2.06V (CY7B991) or VCC/2 (CY7B992).

24.tPWH is measured at 2.0V for the CY7B991 and 0.8 VCC for the CY7B992. tPWL is measured at 0.8V for the CY7B991 and 0.2 VCC for the CY7B992.

25.tORISE and tOFALL measured between 0.8V and 2.0V for the CY7B991 or 0.8VCC and 0.2VCC for the CY7B992.

26.tLOCK is the time that is required before synchronization is achieved. This specification is valid only after VCC is stable and within normal operating limits.

This parameter is measured from the application of a new signal or frequency at REF or FB until tPD is within specified limits.

[+] Feedback