CY7C604XX

Document Number: 001-12395 Rev *H Page 18 of 30

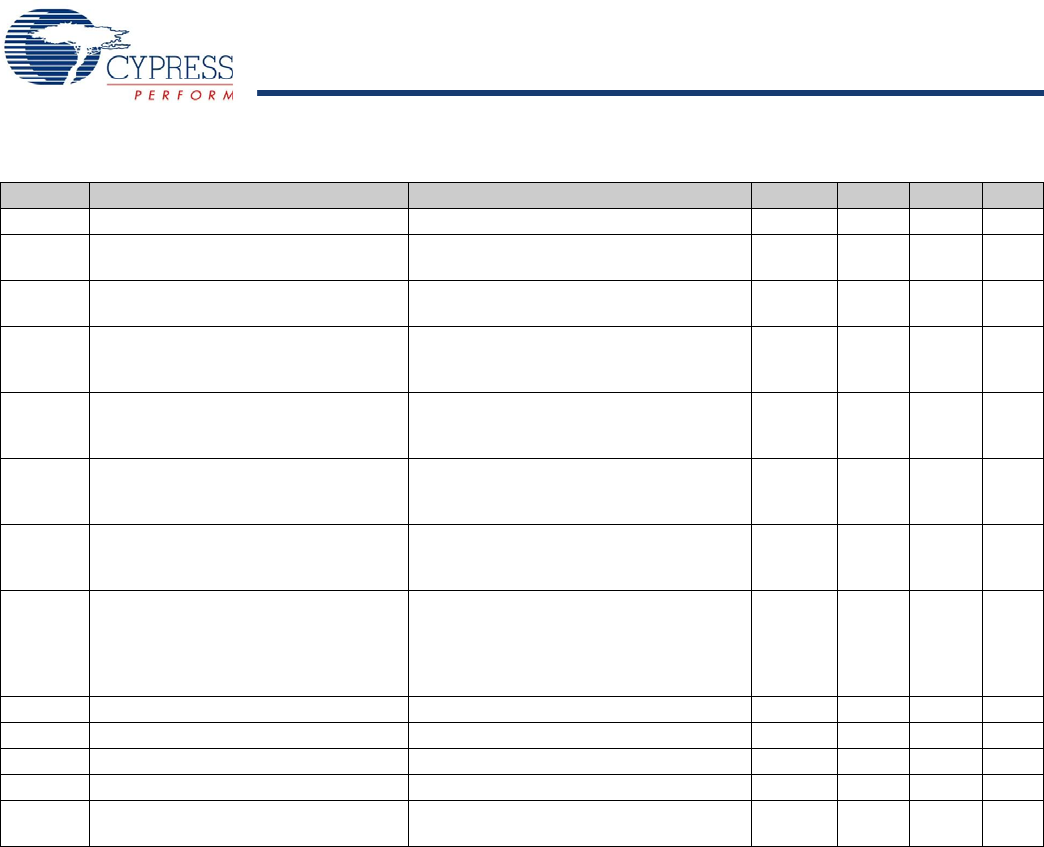

Table 11. 2.4V to 3.0V DC GPIO Specifications

Symbol Description Conditions Min Typ Max Units

R

PU

Pull Up Resistor 4 5.6 8 kΩ

V

OH1

High Output Voltage

Port 2 or 3 Pins

IOH < 10 μA, maximum of 10 mA source

current in all I/Os

Vdd - 0.2 – – V

V

OH2

High Output Voltage

Port 2 or 3 Pins

IOH = 0.2 mA, maximum of 10 mA source

current in all I/Os

Vdd - 0.4 – – V

V

OH3

High Output Voltage

Port 0 or 1 Pins with LDO Regulator

Disabled for Port 1

IOH < 10 μA, maximum of 10 mA source

current in all I/Os

Vdd - 0.2 – – V

V

OH4

High Output Voltage

Port 0 or 1 Pins with LDO Regulator

Disabled for Port 1

IOH = 2 mA, maximum of 10 mA source

current in all I/Os

Vdd - 0.5 – – V

V

OH5A

High Output Voltage

Port 1 Pins with LDO Enabled for 1.8V

Out

IOH < 10 μA, Vdd > 2.4V, maximum of 20

mA source current in all I/Os.

1.50 1.80 2.10 V

V

OH6A

High Output Voltage

Port 1 Pins with LDO Enabled for 1.8V

Out

IOH = 1 mA, Vdd > 2.4V, maximum of 20

mA source current in all I/Os

1.20 – – V

V

OL

Low Output Voltage IOL = 10 mA, maximum of 30 mA sink

current on even port pins (for example,

P0[2] and P1[4]) and 30 mA sink current

on odd port pins (for example, P0[3] and

P1[5])

––0.75V

V

IL

Input Low Voltage – – 0.72 V

V

IH

Input High Voltage 1.6 – V

V

H

Input Hysteresis Voltage – 80 – mV

I

IL

Input Leakage (Absolute Value) – 0.001 1 µA

C

PIN

Capacitive Load on Pins Package and pin dependent

Temp = 25

o

C

0.5

1.7 5 pF

[+] Feedback