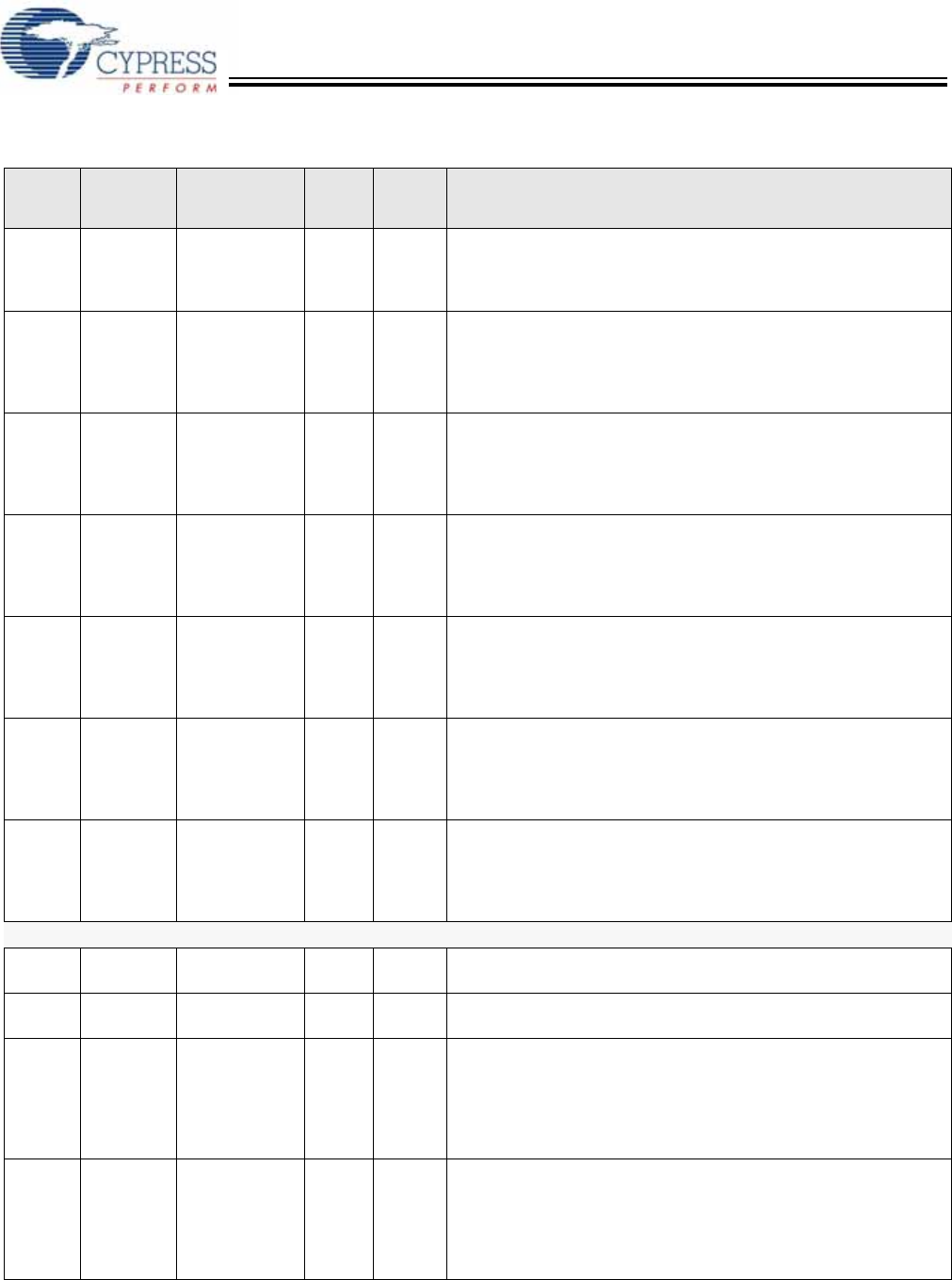

CY7C68033/CY7C68034

Document #: 001-04247 Rev. *D Page 17 of 33

46 PD1 or

FD[9]

CE1# I/O/Z I

(PD1)

Multiplexed pin whose function is selected by the IFCONFIG[1:0]

and EPxFIFOCFG.0 (wordwide) bits.

FD[9] is the bidirectional FIFO/GPIF data bus.

CE1# is a NAND chip enable output signal.

47 PD2 or

FD[10]

CE2# or GPIO2 I/O/Z I

(PD2)

Multiplexed pin whose function is selected by the IFCONFIG[1:0]

and EPxFIFOCFG.0 (wordwide) bits.

FD[10] is the bidirectional FIFO/GPIF data bus.

CE2# is a NAND chip enable output signal.

GPIO2 is a general purpose I/O signal.

48 PD3 or

FD[11]

CE3# or GPIO3 I/O/Z I

(PD3)

Multiplexed pin whose function is selected by the IFCONFIG[1:0]

and EPxFIFOCFG.0 (wordwide) bits.

FD[11] is the bidirectional FIFO/GPIF data bus.

CE3# is a NAND chip enable output signal.

GPIO3 is a general purpose I/O signal.

49 PD4 or

FD[12]

CE4# or GPIO4 I/O/Z I

(PD4)

Multiplexed pin whose function is selected by the IFCONFIG[1:0]

and EPxFIFOCFG.0 (wordwide) bits.

FD[12] is the bidirectional FIFO/GPIF data bus.

CE4# is a NAND chip enable output signal.

GPIO4 is a general purpose I/O signal.

50 PD5 or

FD[13]

CE5# or GPIO5 I/O/Z I

(PD5)

Multiplexed pin whose function is selected by the IFCONFIG[1:0]

and EPxFIFOCFG.0 (wordwide) bits.

FD[13] is the bidirectional FIFO/GPIF data bus.

CE5# is a NAND chip enable output signal.

GPIO5 is a general purpose I/O signal.

51 PD6 or

FD[14]

CE6# or GPIO6 I/O/Z I

(PD6)

Multiplexed pin whose function is selected by the IFCONFIG[1:0]

and EPxFIFOCFG.0 (wordwide) bits.

FD[14] is the bidirectional FIFO/GPIF data bus.

CE6# is a NAND chip enable output signal.

GPIO6 is a general purpose I/O signal.

52 PD7 or

FD[15]

CE7# or GPIO7 I/O/Z I

(PD7)

Multiplexed pin whose function is selected by the IFCONFIG[1:0]

and EPxFIFOCFG.0 (wordwide) bits.

FD[15] is the bidirectional FIFO/GPIF data bus.

CE7# is a NAND chip enable output signal.

GPIO7 is a general purpose I/O signal.

Power and Ground

3

7

AVCC N/A Power N/A Analog V

CC

. Connect this pin to 3.3V power source. This signal

provides power to the analog section of the chip.

6

10

AGND N/A Ground N/A Analog Ground. Connect to ground with as short a path as

possible.

11

17

27

32

43

55

VCC N/A Power N/A V

CC

. Connect to 3.3V power source.

12

26

28

41

53

56

GND N/A Ground N/A Ground.

Table 8. NX2LP-Flex Pin Descriptions (continued)

[6]

56 QFN

Pin

Number

Default Pin

Name

NAND

Firmware

Usage

Pin

Type

Default

State

Description

[+] Feedback