CY7C68033/CY7C68034

Document #: 001-04247 Rev. *D Page 26 of 33

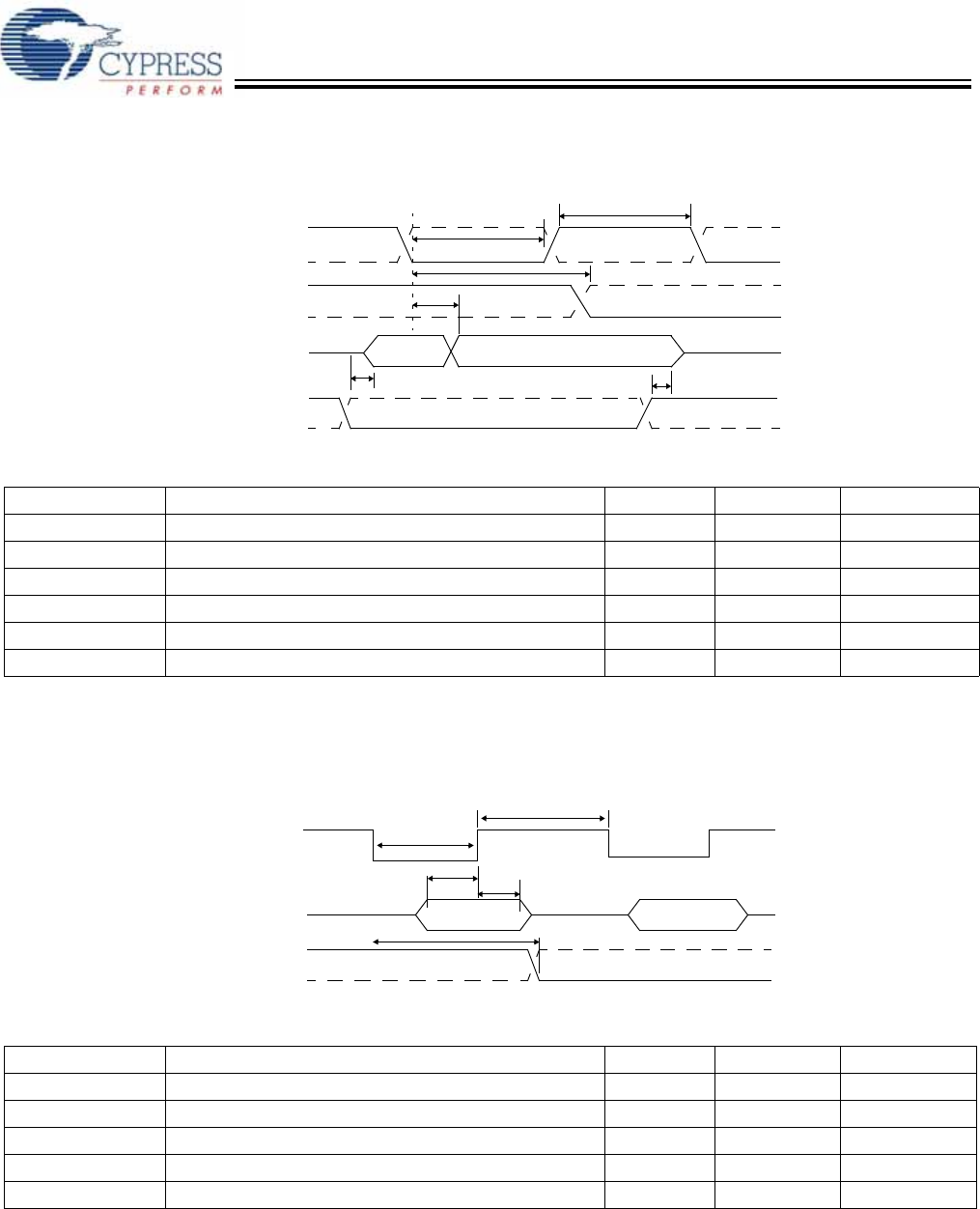

Slave FIFO Asynchronous Read

Figure 11. Slave FIFO Asynchronous Read Timing Diagram

[13]

Slave FIFO Asynchronous Write

Figure 12. Slave FIFO Asynchronous Write Timing Diagram

[13]

Table 11.Slave FIFO Asynchronous Read Parameters

[15]

Parameter Description Min. Max. Unit

t

RDpwl

SLRD Pulse Width LOW 50 ns

t

RDpwh

SLRD Pulse Width HIGH 50 ns

t

XFLG

SLRD to FLAGS Output Propagation Delay 70 ns

t

XFD

SLRD to FIFO Data Output Propagation Delay 15 ns

t

OEon

SLOE Turn-on to FIFO Data Valid 10.5 ns

t

OEoff

SLOE Turn-off to FIFO Data Hold 10.5 ns

SLRD

FLAGS

t

RDpwl

t

RDpwh

SLOE

t

XFLG

t

XFD

DATA

t

OEon

t

OEoff

N+1

N

DATA

t

SFD

t

FDH

FLAGS

t

XFD

SLWR/SLCS#

t

WRpwh

t

WRpwl

Notes

13.Dashed lines denote signals with programmable polarity.

14.GPIF asynchronous RDY

x

signals have a minimum setup time of 50 ns when using internal 48-MHz IFCLK.

15.Slave FIFO asynchronous parameter values use internal IFCLK setting at 48 MHz.

Table 12.Slave FIFO Asynchronous Write Parameters with Internally Sourced IFCLK

[15]

Parameter Description Min. Max. Unit

t

WRpwl

SLWR Pulse LOW 50 ns

t

WRpwh

SLWR Pulse HIGH 70 ns

t

SFD

SLWR to FIFO DATA Setup Time 10 ns

t

FDH

FIFO DATA to SLWR Hold Time 10 ns

t

XFD

SLWR to FLAGS Output Propagation Delay 70 ns

[+] Feedback