CY7C68033/CY7C68034

Document #: 001-04247 Rev. *D Page 27 of 33

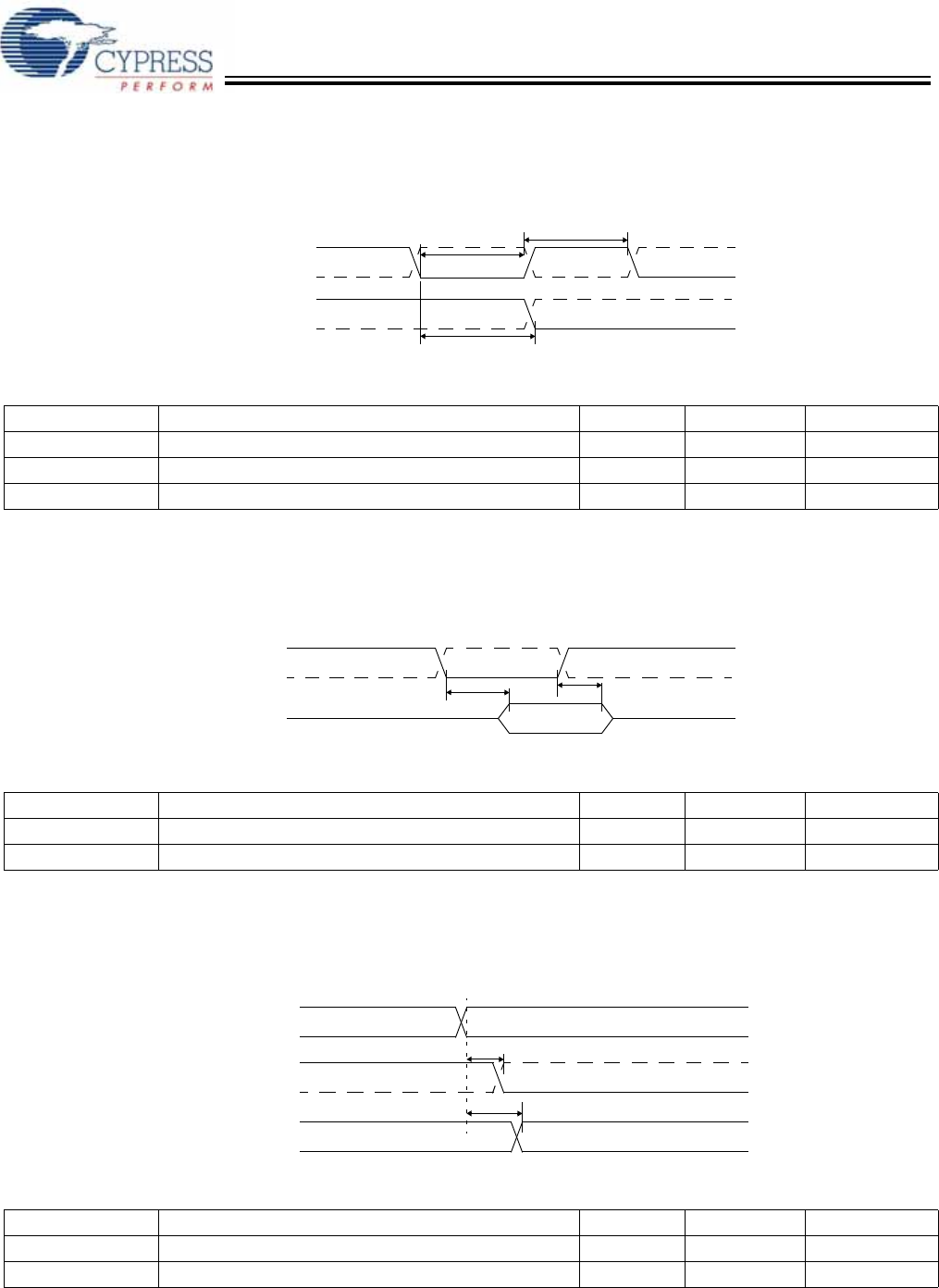

Slave FIFO Asynchronous Packet End Strobe

Figure 13. Slave FIFO Asynchronous Packet End Strobe Timing Diagram

[9]

Slave FIFO Output Enable

Figure 14. Slave FIFO Output Enable Timing Diagram

[13]

Slave FIFO Address to Flags/Data

Figure 15. Slave FIFO Address to Flags/Data Timing Diagram

[13]

Table 13.Slave FIFO Asynchronous Packet End Strobe Parameters

[15]

Parameter Description Min. Max. Unit

t

PEpwl

PKTEND Pulse Width LOW 50 ns

t

PWpwh

PKTEND Pulse Width HIGH 50 ns

t

XFLG

PKTEND to FLAGS Output Propagation Delay 115 ns

Table 14.Slave FIFO Output Enable Parameters

Parameter Description Min. Max. Unit

t

OEon

SLOE Assert to FIFO DATA Output 10.5 ns

t

OEoff

SLOE Deassert to FIFO DATA Hold 10.5 ns

Table 15.Slave FIFO Address to Flags/Data Parameters

Parameter Description Min. Max. Unit

t

XFLG

FIFOADR[1:0] to FLAGS Output Propagation Delay 10.7 ns

t

XFD

FIFOADR[1:0] to FIFODATA Output Propagation Delay 14.3 ns

FLAGS

t

XFLG

PKTEND

t

PEpwl

t

PEpwh

SLOE

DATA

t

OEon

t

OEoff

FIFOADR [1.0]

DATA

t

XFLG

t

XFD

FLAGS

NN+1

[+] Feedback