CY8C24094, CY8C24794

CY8C24894, CY8C24994

Document Number: 38-12018 Rev. *M Page 36 of 47

10.0.5 AC Programming Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

A

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ T

A

≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

are for design guidance only.

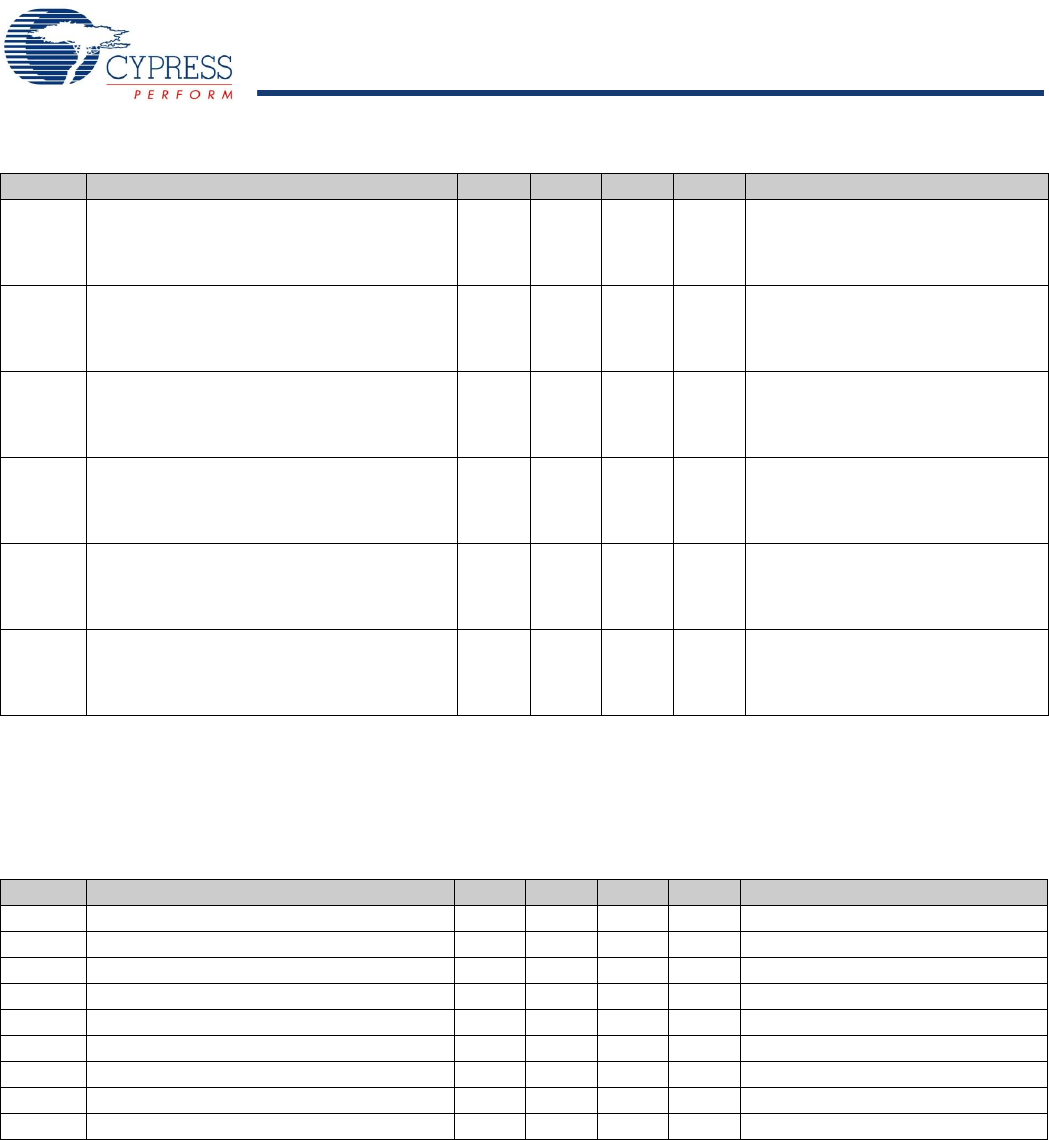

Table 10-25. 3.3V AC Analog Output Buffer Specifications

Symbol Description Min Typ Max Units Notes

T

ROB

Rising Settling Time to 0.1%, 1V Step, 100 pF

Load

Power = Low

Power = High

–

–

–

–

3.8

3.8

μs

μs

T

SOB

Falling Settling Time to 0.1%, 1V Step, 100 pF

Load

Power = Low

Power = High

–

–

–

–

2.6

2.6

μs

μs

SR

ROB

Rising Slew Rate (20% to 80%), 1V Step, 100

pF Load

Power = Low

Power = High

0.5

0.5

–

–

–

–

V/μs

V/μs

SR

FOB

Falling Slew Rate (80% to 20%), 1V Step, 100

pF Load

Power = Low

Power = High

0.5

0.5

–

–

–

–

V/μs

V/μs

BW

OBSS

Small Signal Bandwidth, 20mV

pp

, 3dB BW,

100 pF Load

Power = Low

Power = High

0.7

0.7

–

–

–

–

MHz

MHz

BW

OBLS

Large Signal Bandwidth, 1V

pp

, 3dB BW, 100

pF Load

Power = Low

Power = High

200

200

–

–

–

–

kHz

kHz

Table 10-26. AC Programming Specifications

Symbol Description Min Typ Max Units Notes

T

RSCLK

Rise Time of SCLK 1 – 20 ns

T

FSCLK

Fall Time of SCLK 1 – 20 ns

T

SSCLK

Data Set up Time to Falling Edge of SCLK 40 – – ns

T

HSCLK

Data Hold Time from Falling Edge of SCLK 40 – – ns

F

SCLK

Frequency of SCLK 0 – 8 MHz

T

ERASEB

Flash Erase Time (Block) – 10 – ms

T

WRITE

Flash Block Write Time – 30 – ms

T

DSCLK

Data Out Delay from Falling Edge of SCLK – – 45 ns Vdd > 3.6

T

DSCLK3

Data Out Delay from Falling Edge of SCLK – – 50 ns 3.0 ≤ Vdd ≤ 3.6

[+] Feedback