STK14C88-5

Document Number: 001-51038 Rev. ** Page 5 of 17

Data Protection

The STK14C88-5 protects data from corruption during low

voltage conditions by inhibiting all externally initiated STORE

and WRITE operations. The low voltage condition is detected

when V

CC

is less than V

SWITCH

. If the STK14C88-5 is in a

WRITE mode (both CE

and WE are low) at power up after a

RECALL or after a STORE, the WRITE is inhibited until a

negative transition on CE or WE is detected. This protects

against inadvertent writes during power up or brown out condi-

tions.

Noise Considerations

The STK14C88-5 is a high speed memory. It must have a high

frequency bypass capacitor of approximately 0.1 µF connected

between V

CC

and V

SS,

using leads and traces that are as short

as possible. As with all high speed CMOS ICs, careful routing of

power, ground, and signals reduce circuit noise.

Hardware Protect

The STK14C88-5 offers hardware protection against inadvertent

STORE operation and SRAM WRITEs during low voltage condi-

tions. When V

CAP

<V

SWITCH

, all externally initiated STORE

operations and SRAM WRITEs are inhibited. AutoStore can be

completely disabled by tying VCC to ground and applying + 5V

to V

CAP

. This is the AutoStore Inhibit mode; in this mode,

STOREs are only initiated by explicit request using either the

software sequence or the HSB

pin.

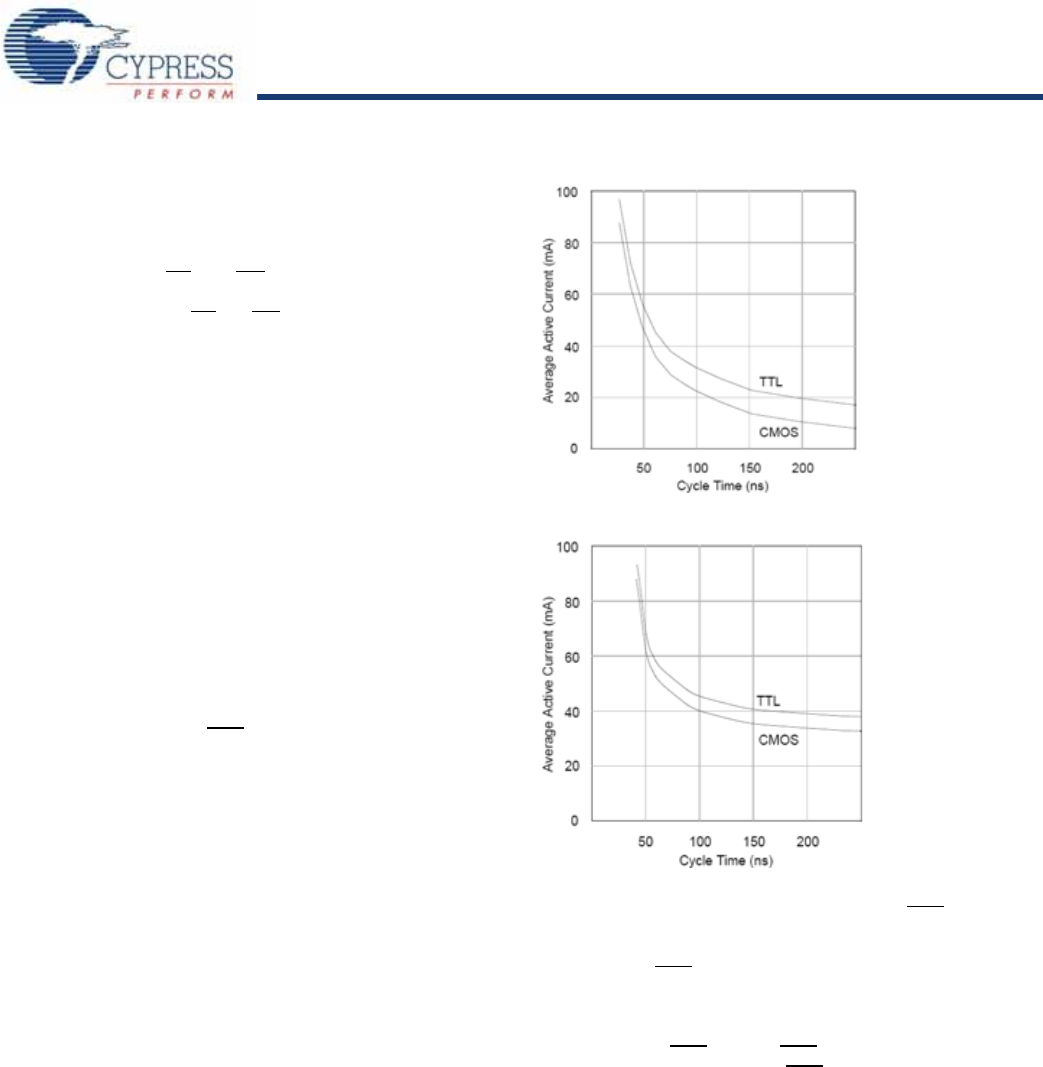

Low Average Active Power

CMOS technology provides the STK14C88-5 the benefit of

drawing significantly less current when it is cycled at times longer

than 50 ns. Figure 5 and Figure 6 shows the relationship

between I

CC

and READ or WRITE cycle time. Worst case current

consumption is shown for both CMOS and TTL input levels

(commercial temperature range, VCC = 5.5V, 100% duty cycle

on chip enable). Only standby current is drawn when the chip is

disabled. The overall average current drawn by the STK14C88-5

depends on the following items:

■ The duty cycle of chip enable

■ The overall cycle rate for accesses

■ The ratio of READs to WRITEs

■ CMOS versus TTL input levels

■ The operating temperature

■ The V

CC

level

■ IO loading

Preventing Store

The STORE function is disabled by holding HSB high with a

driver capable of sourcing 30 mA at a V

OH

of at least 2.2V,

because it has to overpower the internal pull down device. This

device drives HSB

LOW for 20 μs at the onset of a STORE.

When the STK14C88-5 is connected for AutoStore operation

(system V

CC

connected to V

CC

and a 68 μF capacitor on V

CAP

)

and V

CC

crosses V

SWITCH

on the way down, the STK14C88-5

attempts to pull HSB

LOW. If HSB does not actually get below

V

IL

, the part stops trying to pull HSB LOW and abort the STORE

attempt.

Figure 5. Current Versus Cycle Time (READ)

Figure 6. Current Versus Cycle Time (WRITE)

[+] Feedback