EM78P458/459

OTP ROM

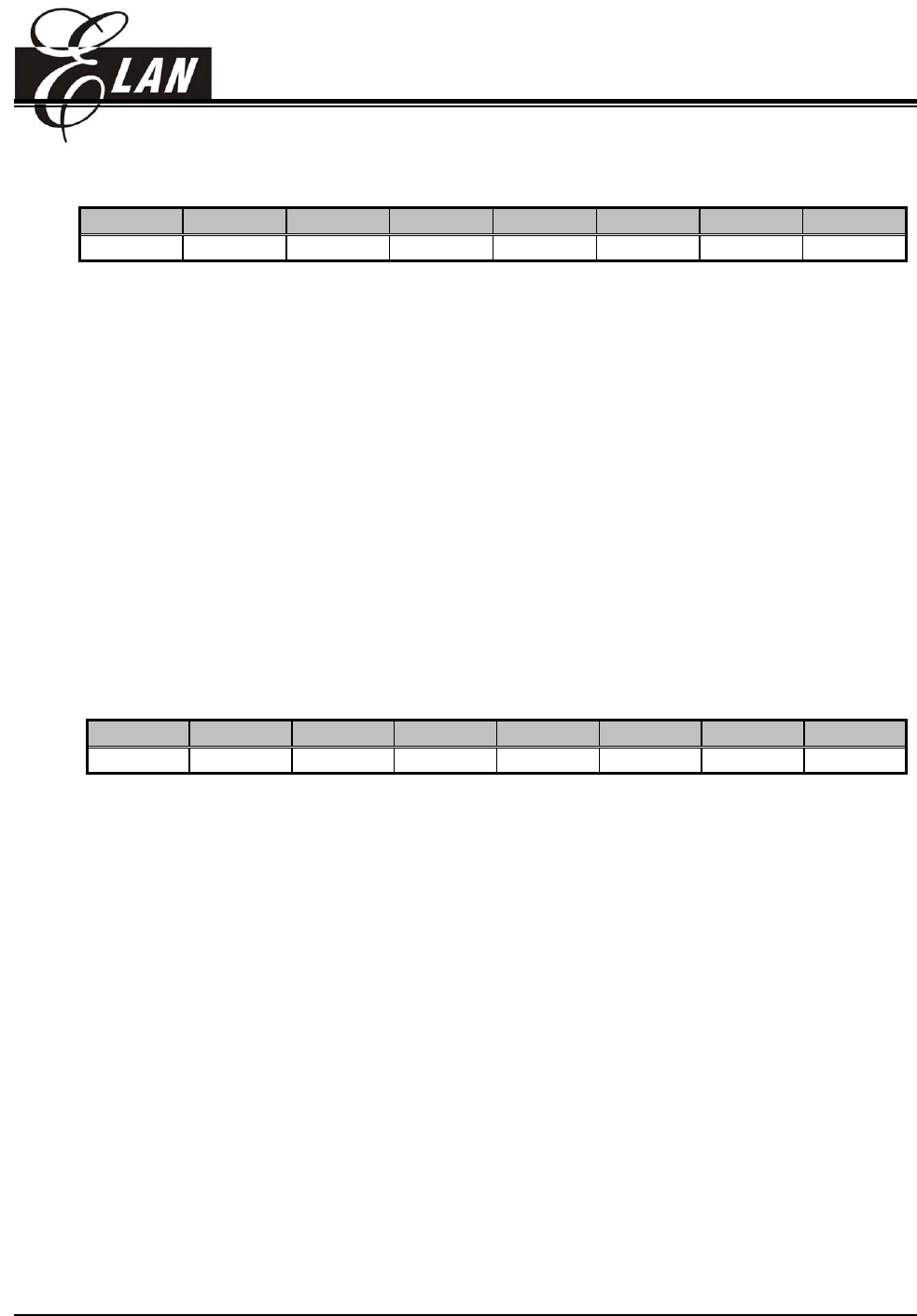

9. IOCE0 (WDT Control Register)

7 6 5 4 3 2 1 0

WDTE EIS - - - - - -

• Bit 7 (WDTE) Control bit is used to enable Watchdog Timer.

0: Disable WDT;

1: Enable WDT.

WDTE is both readable and writable

• Bit 6 (EIS) Control bit is used to define the function of the P50 (/INT) pin.

0: P50, input pin only;

1: /INT, external interrupt pin. In this case, the I/O control bit of P50 (bit 0 of IOC50) must be set to

"1".

When EIS is "0", the path of /INT is masked. When EIS is "1", the status of /INT pin can also be read

by way of reading Port 5 (R5). Refer to Fig. 7.

EIS is both readable and writable.

• Bits 0~5 Not used.

10. IOCF0 (Interrupt Mask Register)

7 6 5 4 3 2 1 0

- CMPIE PWM2IE PWM1IE ADIE EXIE ICIE TCIE

• Bit 0 (TCIE) TCIF interrupt enable bit.

0: disable TCIF interrupt

1: enable TCIF interrupt

• Bit 1 (ICIE) ICIF interrupt enable bit.

0: disable ICIF interrupt

1: enable ICIF interrupt

• Bit 2 (EXIE) EXIF interrupt enable bit.

0: disable EXIF interrupt

1: enable EXIF interrupt

• Bit 3 (ADIE) ADIF interrupt enable bit.

0: disable ADIF interrupt

1: enable ADIF interrupt

• Bit 4 (PWM1IE) PWM1IF interrupt enable bit.

0: disable PWM1 interrupt

1: enable PWM1 interrupt

This specification is subject to change without prior notice. 07.01.2003 (V1.3)

18