Chapter 3 Programming

IPMC7126E/7616E I/O Module Installation and Use (6806800A45B)

23

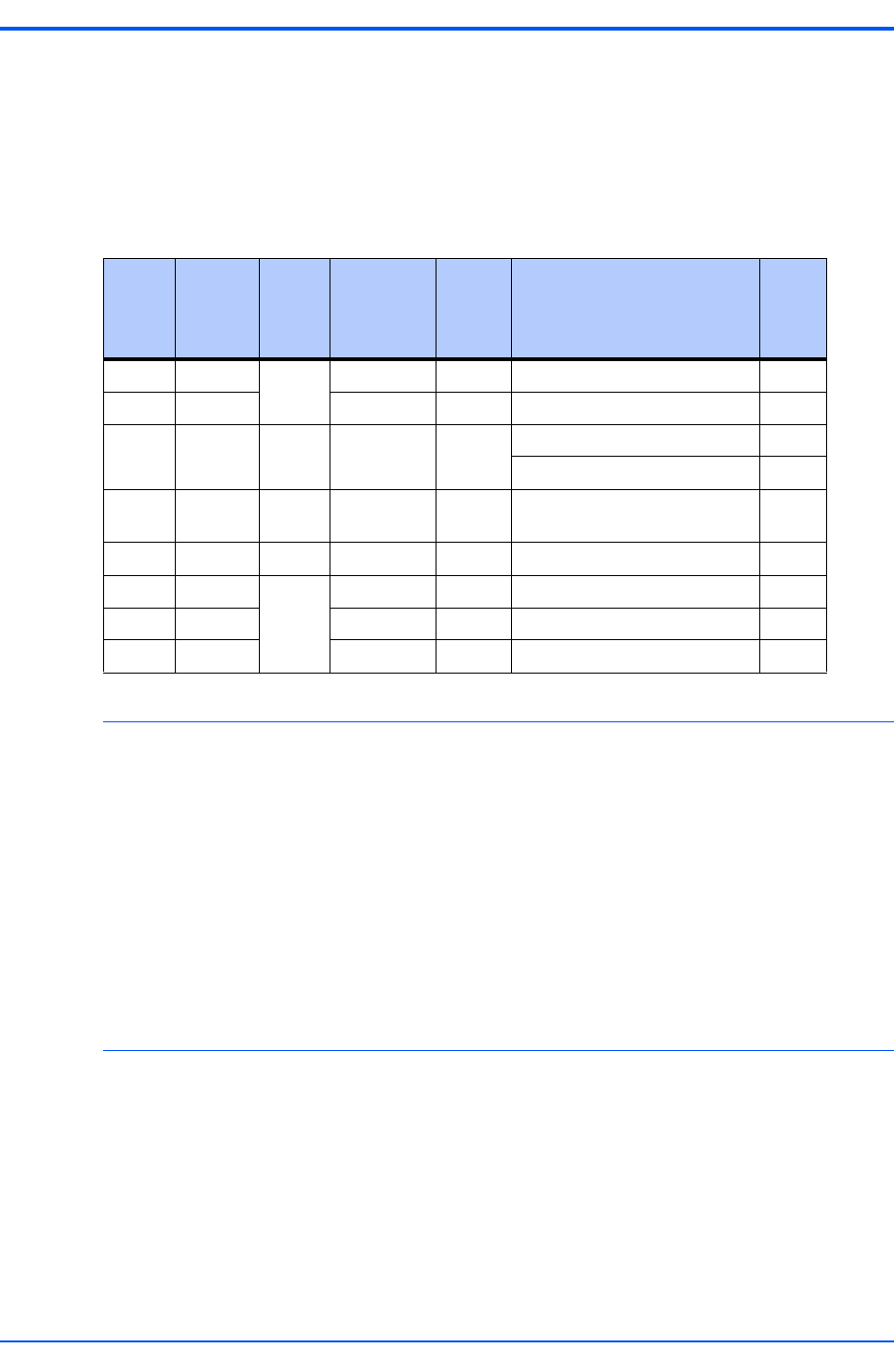

Interrupt Routing to PIB

Module interrupts and MVME5100 Ethernet Port 2 interrupts go through the 8259 pair and into

the PIB. The output of the PIB then goes to the Hawk MPIC on the MVME5100. The table below

lists the ISA interrupts routed to the PIB.

Notes

1. Internally generated by the PIB.

2. After a reset, all ISA IRQ interrupt lines default to

edge-sensitive mode.

3. Interrupts from the Z8536 and Z85230 devices are externally wired. External logic will

determine which device to acknowledge during a pseudo IACK cycle. The Z8536 CIO has

higher priority than the Z85230 ESCC. This IRQ MUST be programmed for level-sensitive

mode.

4. This interrupt is routed from the MVME5100 through the IPMC connector to the module’s

PIB to allow backward compatibility to other products.

Table 3-11. PIB Interrupt Assignments

PRI

ISA

IRQ

Controller

Edge/Leve

l

Polarity

Interrupt Source

Notes

1 IRQ0 INT1 Edge High Timer 1 / Counter 0 1

3-10 IRQ2 Edge High Cascade Interrupt from INT2

4 IRQ9 INT2 Level High Z8536 CIO 2,3

Z85230 ESCC

5 IRQ10 INT2 Level Low PCI-Ethernet Interrupt (from

MVME5100 Port 2)

2,4

9 IRQ14 INT2 Level Low PCI-SCSI Interrupt 2

11 IRQ3 INT1 Edge High COM2 (Async Serial Port 2)

12 IRQ4 Edge High COM1 (Async Serial Port 1)

15 IRQ7 Edge High Parallel Port Interrupt