4.3 Interface Register

C156-E227-01EN 4-11

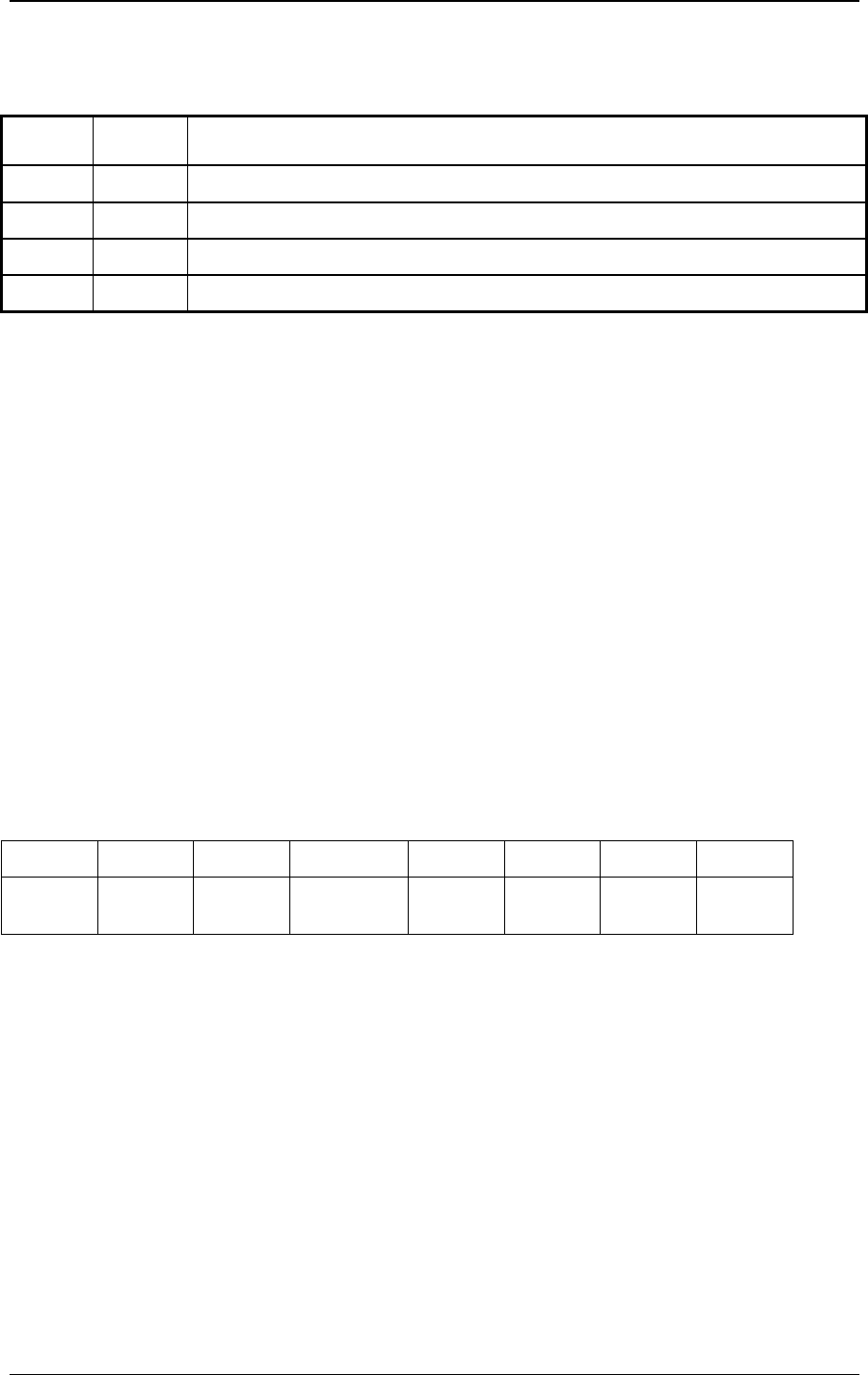

Table 4.12 I/O and C/D

I/O C/D Meaning

0 1 Packet command transfer

1 0 Data or parameter transfer (from the ODD to the host)

0 0 Data or parameter transfer (from the host to the ODD)

1 1 The completion status in the Status register is effective.

4.3.1.13 Sector Number register

This register is not used. The ODD ignores all specified values.

4.3.1.14 ATAPI Status register

This register indicates the status of the ODD. It is updated to reflect the current

ODD status and the progress of the current command. When the BSY bit is 0,

other bits of the register are effective and some other command block registers

may be set with significant information. When the BSY bit is 1, the other bits of

this register and all other command block registers are ineffective.

While the ODD is in sleep mode, the ATAPI Status register and all other

command block registers are ineffective.

If the host reads this register during interrupt pending, the interrupt is cleared.

Table 4.13 Bit definitions of ATAPI Status register

765 4 3210

BSY DRDY

Reserved

(0b)

SERVICE DRQ

CORR

(0b)

Reserved

(0b)

CHECK Read

•

BSY (Busy) is set during command block register control. When BSY is 1,

the ODD ignores all command block registers other than the Device Reset

command.

The ODD updates the DRQ and CHECK values only when BSY is 1. After the

final block of the PIO data-in command is transferred, the BSY bit setting is

canceled and the DRQ bit is cleared.

When BSY is 0, the ODD may update the SERVICE bit of the ATAPI Status

register and the Data register. The ODD does not update all other command block

registers and the ATAPI Status register bits.