42

2 System Board

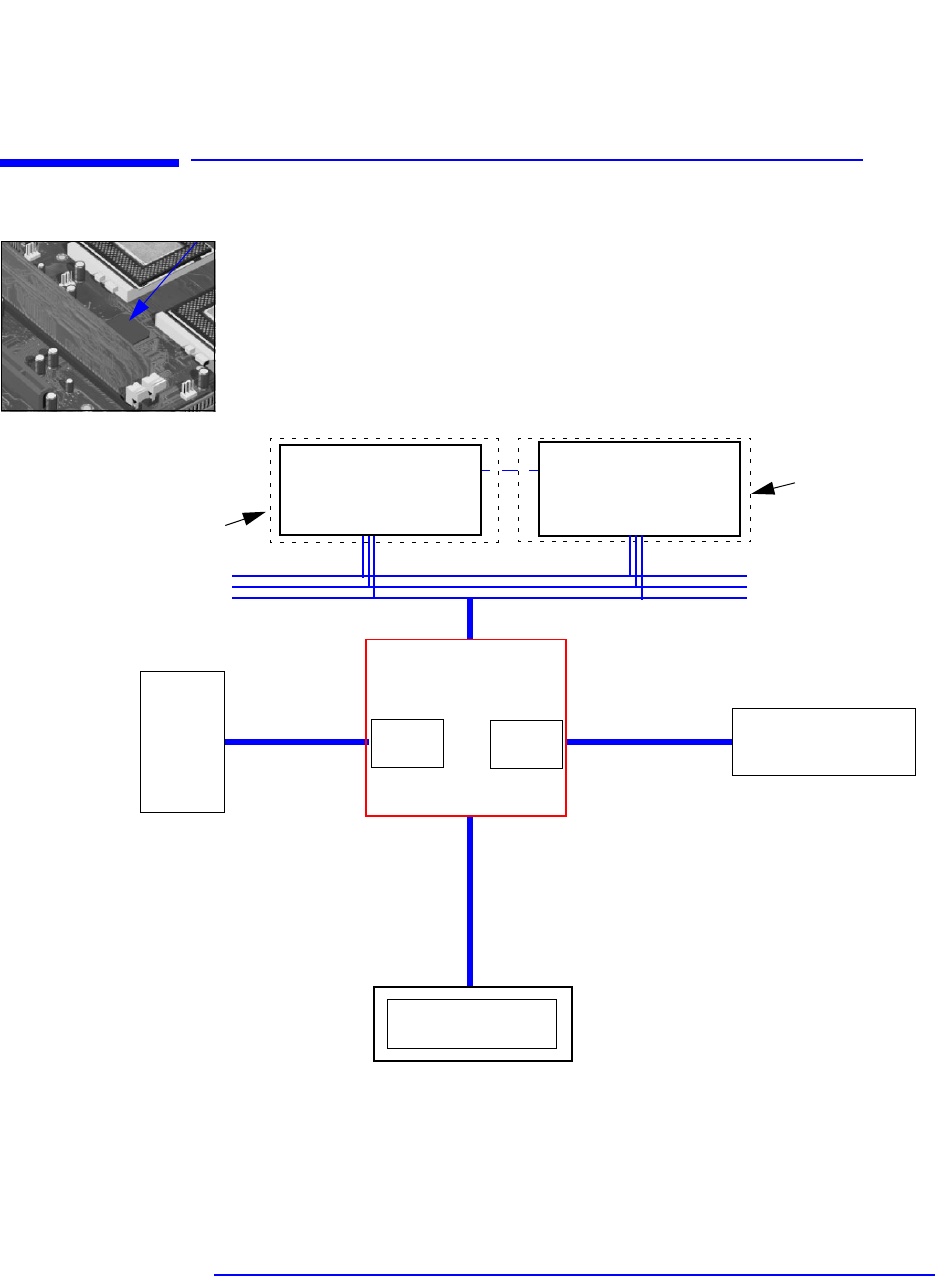

Memory Controller Hub (MCH) 82820

Memory Controller Hub (MCH) 82820

The MCH Host Bridge/Controller is contained in a 324-pin Ball Grid Array

(BGA) package and is the bridge between the Host bus, Direct Rambus

channel (main memory), AGP 4x graphic bus, Hub Link 8-bit and Hub Link

16-bit.

The following figure shows an example of the system block diagram using

the MCH.

The following table shows the features that are available in the MCH Host

Bridge/Controller.

820 Memory

Controller Hub (MCH)

82820

AGP

Pro (MT)

or AGP 4x

(DT)

Connector

Direct Rambus

Bus

Address (36)

Control

Data (64)

AGP 4x Bus

(133 MHz 1 GB/s

data transfer rate)

Intel Pentium III

Processor

(optional second processor)

with L2 cache memory

FC-PGA Package

Host (also called FSB) two-

way Bus (100/133 MHz,

1 GB/s data transfer rate)

HUB LINK 8

(266 MB/s data

transfer rate)

Intel Pentium III

Processor

with L2 cache memory

I/O Controller Hub

(ICH) 82801AA

(1.2 GB/s at 300 MHz or

1.6 GB/s at 400 MHz-

data transfer rate)

FC-PGA Package

AGP

Interface

Memory

Controller

Two onboard RIMM sockets

supporting RDRAM memory.