17

3. Transmitter LVDS output pulse position measurement

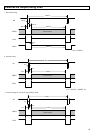

(1) Base configuration

(a) 8bit

D.OUT1

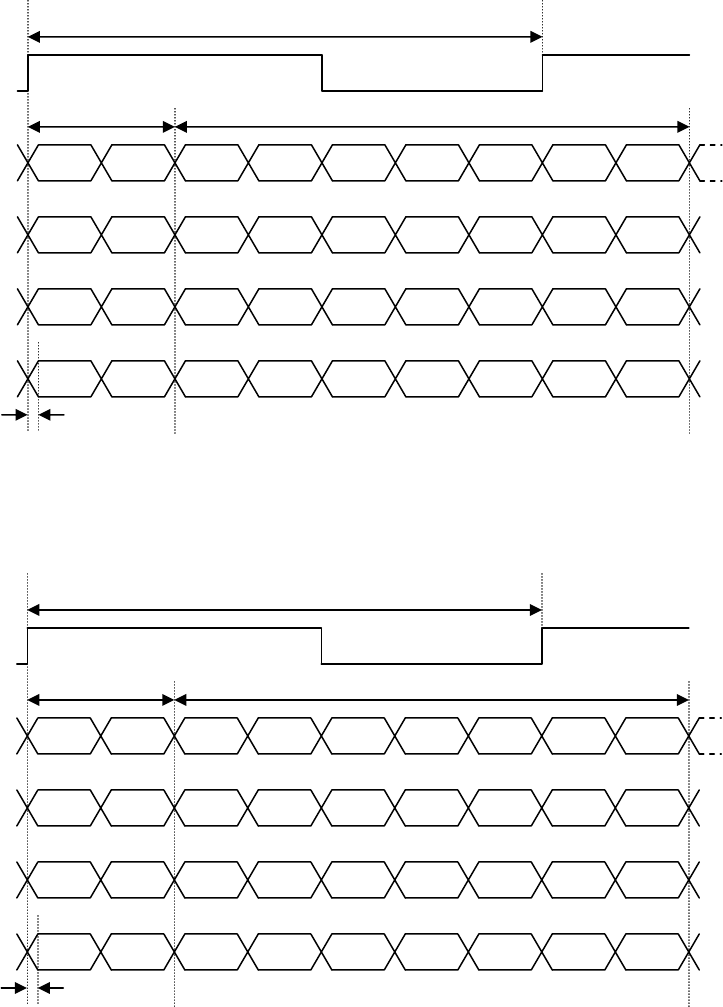

(b) 10bit

D.OUT1

0±3ns

Previous Cycle

T

CLK

15.625ns (64MHz)

1.41V

1.075V

DA7-1 DA6-1 N.C N.C N.C DB7 DB6 DA7 DA6

N.C N.C N.C FVAL LVAL N.C N.C N.C N.C

DB2-1 DB1-1 N.C N.C DB5 DB4 DB3 DB2 DB1

DA1-1 DA0-1 DB0 DA5 DA4 DA3 DA2 DA1 DA0

X3

X2

X1

X0

CLKX

Next Cycle

(

VD

)

(

HD

)

0±3ns

Previous Cycle

T

CLK

15.625ns (64MHz)

1.41V

1.075V

DA7-1 DA6-1 N.C DB7 DB6 N.C N.C DA7 DA6

DB3-1 DB2-1 N.C FVAL LVAL DB5 DB4 DB3 DB2

N.C DA9-1 DB1 DB0 DB9 DB8 N.C N.C DA9

DA1-1 DA0-1 DA8 DA5 DA4 DA3 DA2 DA1 DA0

X3

X2

X1

X0

CLKX

Next Cycle

(

VD

)

(

HD

)