26

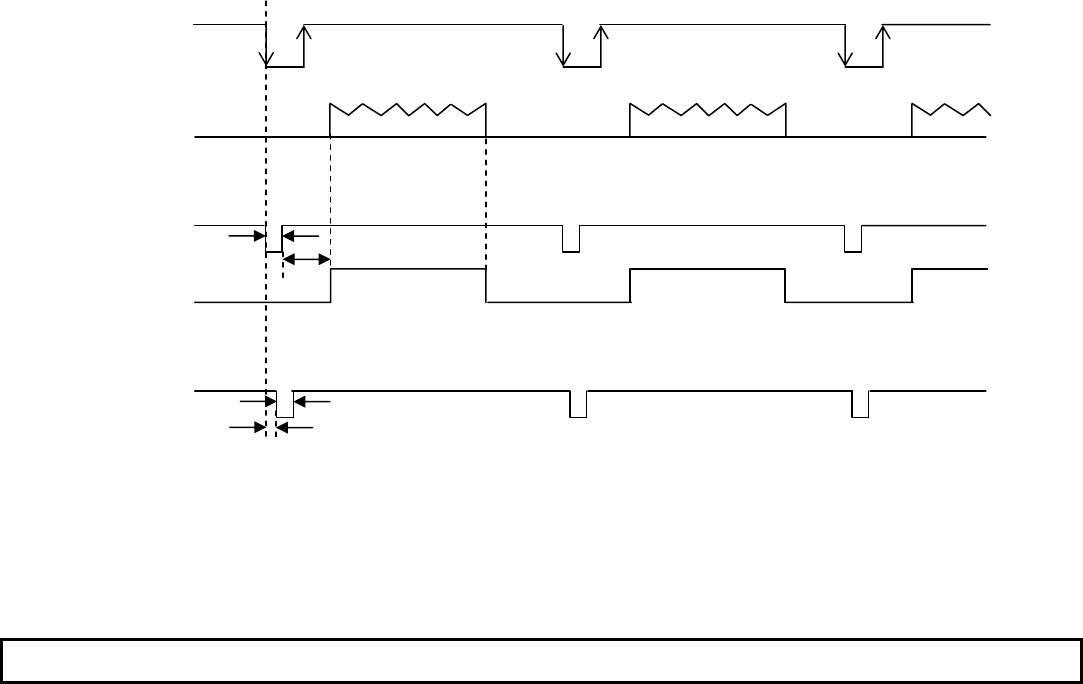

4. VD reset

When external VD pulse is inputted, internal HD/VD is reset.

External VD specification: 16.00 Hz or less

*Note: When external VD of 16.00 Hz or more is input, electronic shutter has an equation between external VD and 16.00 Hz.

*1:When partial scan, variable by start position of picture grabbing.

4H when vertical two pixel addition.

1. Input signal

The level of the trigger signal input to KP-F500PCL/SCL and KP-FR500PCL/SCL is as follows.

(1) Input from CameraLink cable

LVDS level.

(2) Input from 12-pin connector

High level : +2.5 to +5.0 V

Low level : 0 to +0.3 V

2. Output signal

The level of the trigger signal output from KP-F500PCL/SCL and KP-FR500PCL/SCL is as follows.

High level : +5V

Low level : 0V

Input / Output signal

High

Low

Data output

VD

3H

FVAL

8H (*1)

VD input

(Low active)

VD output

3H

0.3

μ

s