Chapter 2. System board features

Video subsystem

The video subsystem includes the Intel 810 graphics controller integrated in the Graphics Memory

Controller Hub (GMCH) and 4MB of 100MHz local graphics display cache SDRAM.

Graphics memory controller hub (Super Video Graphics Array)

The video subsystem uses system memory for display buffer, commands, and 3D textures on

AGP-enabled operating systems via Dynamic Video Memory Technology (DVMT). The Intel 810 graphics

controller drivers will adjust the memory footprint depending on available system memory, current desktop

resolution, and presence of the display cache local memory. DVMT employs direct AGP and intelligent

arbitration to dynamically allocate and deallocate memory for textures for applications requiring additional

texture memory.

The operating system requires allocation of up to 1MB of system memory to support legacy VGA. System

properties will display up to 1MB less than physical system memory available to the operating system.

The integrated graphics memory controller hub supports all video graphics array (VGA) modes and is

compliant with super video graphics array (SVGA) modes and Video Electronics Standards Association

(VESA) 1.2. Some of the features are:

2D and 3D hardware acceleration with hardware cursor

Integrated 230 MHz RAMDAC for up to 1600x1200 at 85Hz resolution

Hardware Motion Compensation via Intel HWMC Software Development Kit

Advanced Power Management (APM)

Advanced Configuration and Power Interface (ACPI)

On Now (Suspend to RAM)

Plug and Play

VESA Display Data Channel version DDC2B

GDI, Direct X, and OpenGL v1.1 Application Programming Interfaces

The integrated graphics memory controller subsystem supports the VESA Display Data Channel (DDC)

standard 1.1 and uses DDC1 and DDC2B to determine optimal values during automatic monitor detection.

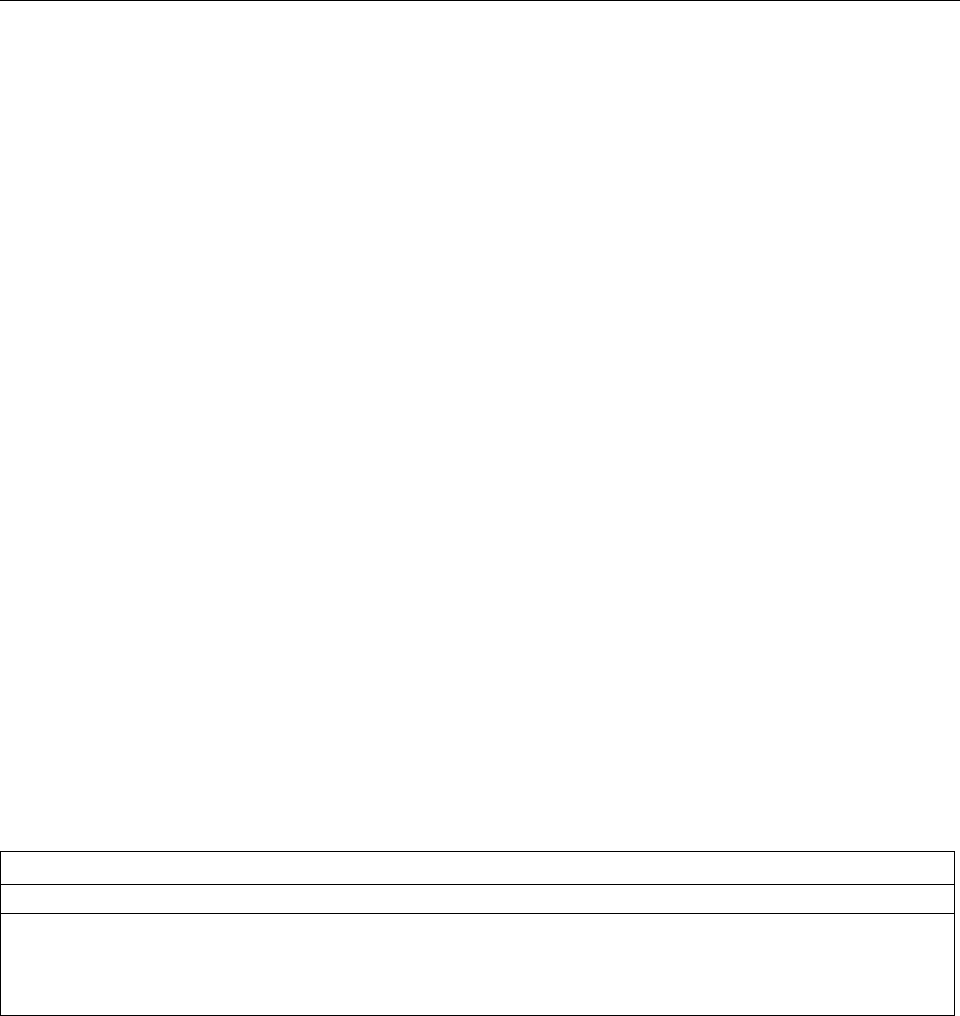

The video subsystem has the following resource assignments:

Figure 2. Video subsystem resources

Resource Assignment

ROM (hex) C0000–C7FFF (32KB)

RAM (hex) A0000–BFFFF

I/O (hex) 3B0–3BB, 3C0–3DF

IRQ PCI interrupt #A (default assigned to ISA IRQ #1)

DMA None

For further information on resource assignments, see Appendix B, “System address maps” on page 36

and Appendix C, “IRQ and DMA channel assignments” on page 40.

6 Technical Information Manual