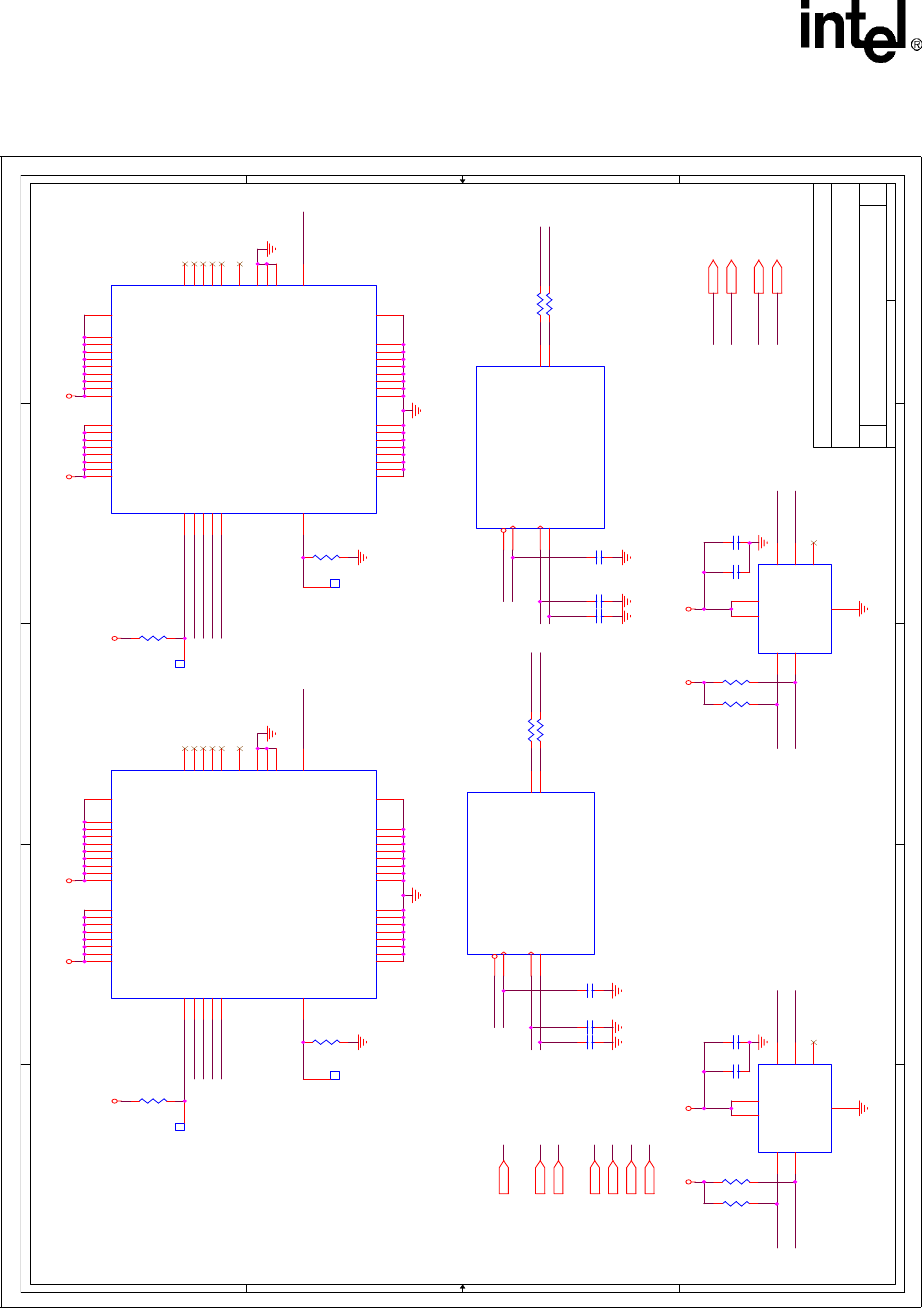

LXD9785 PQFP Demo Board with FPGA for SS-SMII (Fiber)-to-MII Conversion

30 Development Kit Manual

Document #: 249323

Revision #: 003

Rev. Date: January 24, 2002

Figure 15. SS-SMII to MII ALTERA

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

SS-SMII TO MII ALTERA A2

LXD9785 SS/SMII MII FX DV BOARD

B

13 18Wednesday, February 21, 2001

Title

Size Document Number Rev

Date: Sheet

of

REF_CLK_2

RX_CLK

REF_CLK_3

RX_SYNC

nRESET

TX_CLK0

TX_SYNC0

CONF_DONE1DCLK0

DATA0

DCLK1

DATA1nSTATUS1nSTATUS0

CONF_DONE0

CONF_DONE0

nSTATUS0

DATA0

DCLK0

SYNC_FPGA_I

nRESET

REF_CLK_2

TX_SYNC0

TX_CLK0

SYNC_FPGA_O

DATA1

DCLK1

nSTATUS1

CONF_DONE1

SYNC_FPGA_ISYNC_FPGA_O

REF_CLK_3

nRESET

TX_SYNC1

TX_CLK1

RX_CLK1

RX_SYNC1

TX_CLK1

TX_SYNC1

RX_SYNC

RX_CLK

RX_SYNC1

RX_CLK1

REF_CLK_214

RX_CLK3,16

REF_CLK_314

RX_SYNC3,16

nRESET3

TX_CLK0 3,16

TX_SYNC0 3,16

RX_CLK13,16

RX_SYNC13,16

TX_CLK1 3,16

TX_SYNC1 3,16

VCC_EXTVCC_EXTVCC_EXT VCC_EXT

VCC_EXT

GND

VCC_FPGA

VCC_FPGA VCC_FPGA

VCC_EXT

GND

VCC_FPGA

GND

GND

GNDGND

GNDGND

GNDGND

GNDGND

GND

GND

R565

1K

R564

1K

X50 X51

R731 50 1%

R567 50 1%

U33

EPC1PC8

2

3

4

6

1

8

7

5

DCLK

OE

nCS

nCASC

DATA

VCC

VCC

GND

U30F

EP20K100QC208-1_SS_SMII

131

184

188

147

112

27

SS_SMII_RXCLK

SS_SMII_RXSYNC

nRESET

SS_SMII_TXSYNC

SS_SMII_TXCLK

REF_CLK(125 MHz)

U31F

EP20K100QC208-1_SS_SMII

131

184

188

147

112

27

SS_SMII_RXCLK

SS_SMII_RXSYNC

nRESET

SS_SMII_TXSYNC

SS_SMII_TXCLK

REF_CLK(125 MHz)

U30E

EP20K100QC208-1_SS_SMII

10

43

64

95

114

149

169

199

16

24

39

78

118

127

143

183

128

8

53

80

86

136

172

189

208

125

1

23

28

52

79

105

126

156

182

26

25

130

75

76

129

186

180

185

29

83

82

133

132

73 151

GNDIO1

GNDIO2

GNDIO3

GNDIO4

GNDIO5

GNDIO6

GNDIO7

GNDIO8

GNDINT1

GNDINT2

GNDINT3

GNDINT4

GNDINT5

GNDINT6

GNDINT7

GNDINT8

GND_CKLK

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCC_CKLK

VCCINT1

VCCINT2

VCCINT3

VCCINT4

VCCINT5

VCCINT6

VCCINT7

VCCINT8

VCCINT9

MSEL1

MSEL0

nCE

TMS

TCK

TDI

TRST

TDO

nCEO

nCONFIG

CONF_DONE

nSTATUS

DATA0

DCLK

SYNC_FPGA_IN SYNC_FPGA_OUT

U31E

EP20K100QC208-1_SS_SMII

10

43

64

95

114

149

169

199

16

24

39

78

118

127

143

183

128

8

53

80

86

136

172

189

208

125

1

23

28

52

79

105

126

156

182

26

25

130

75

76

129

186

180

185

29

83

82

133

132

73 151

GNDIO1

GNDIO2

GNDIO3

GNDIO4

GNDIO5

GNDIO6

GNDIO7

GNDIO8

GNDINT1

GNDINT2

GNDINT3

GNDINT4

GNDINT5

GNDINT6

GNDINT7

GNDINT8

GND_CKLK

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCC_CKLK

VCCINT1

VCCINT2

VCCINT3

VCCINT4

VCCINT5

VCCINT6

VCCINT7

VCCINT8

VCCINT9

MSEL1

MSEL0

nCE

TMS

TCK

TDI

TRST

TDO

nCEO

nCONFIG

CONF_DONE

nSTATUS

DATA0

DCLK

SYNC_FPGA_IN SYNC_FPGA_OUT

C341

CAP PAD

R29

1K

C340

CAP PAD

R550

1K

C344

CAP PAD

C182

0.1uF

C343

CAP PAD

C155

0.01uF

C342

CAP PAD

R551

1K

C345

CAP PAD

R28

1K

R549

1K

C183

0.01uF

C154

0.1uF

U6

EPC1PC8

2

3

4

6

1

8

7

5

DCLK

OE

nCS

nCASC

DATA

VCC

VCC

GND

X34

R27

1K

R563 50 1%

R562 50 1%

X35