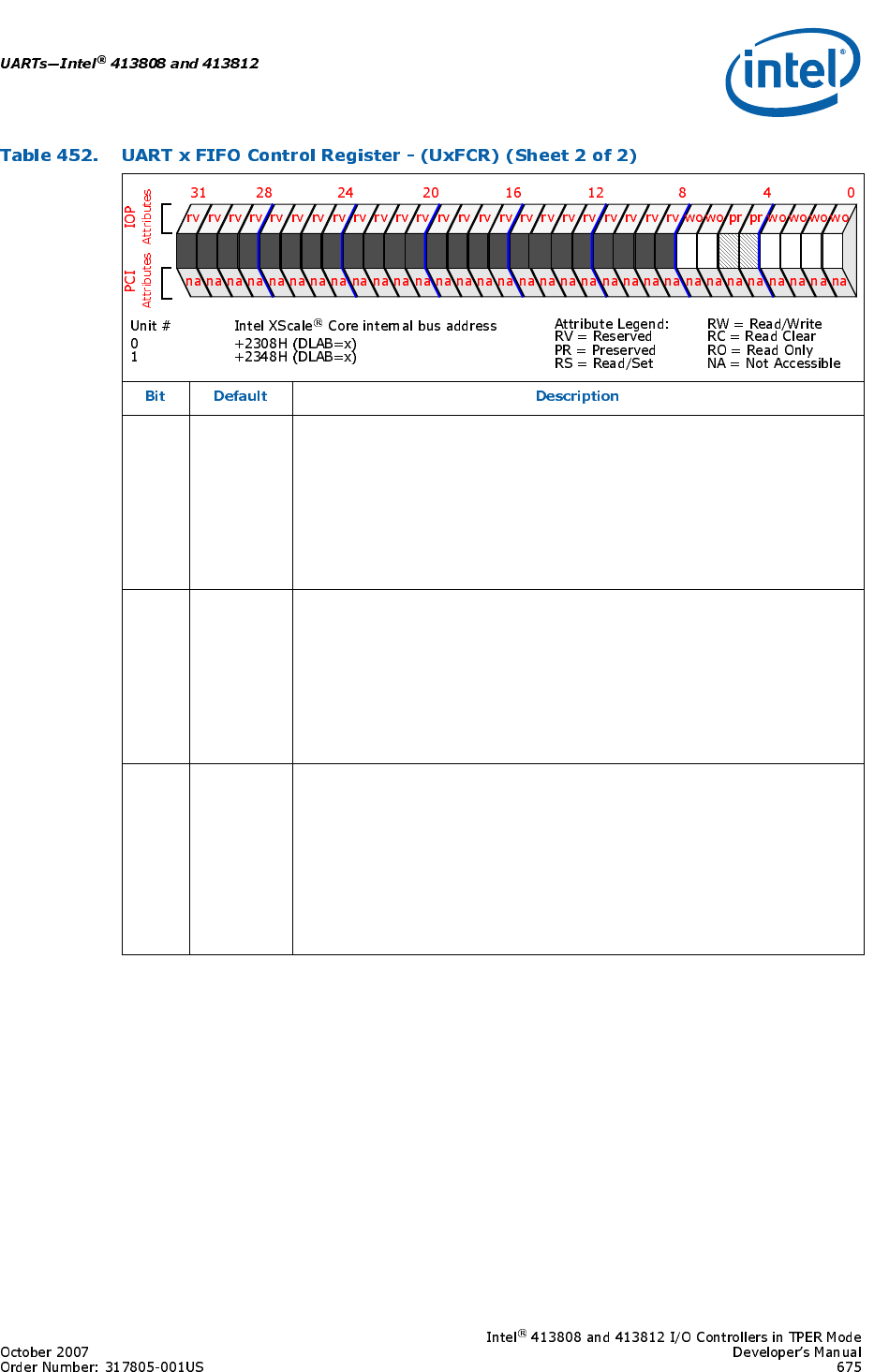

20

2

Reset Transmitter FIFO (RESETTF): When set, the Transmitter FIFO counter is

reset to clear all the bytes in the FIFO. The TDRQ bit of LSR is set generating a

Transmitter Requests Data Interrupt IID field of IIR when the TIE bit in the IER

register is set. The Transmitter Shift register is not reset; it completes the current

transmission. Any transmit FIFO Service-Request Interrupts are cleared.

Note: After the FIFO is cleared, RESETTF is automatically reset to 0.

0 = no effect

1 = The transmitter FIFO is cleared (FIFO counter set to 0). After clearing, bit is

automatically reset to 0

10

2

Reset Receiver FIFO (RESETRF): When set, the receiver FIFO counter is reset to

clear all the bytes in the FIFO. The DR bit in LSR is reset to 0. All the error bits in the

FIFO and the FIFOE bit in LSR are cleared. Any error bits (OE, PE, FE or BI), that

had been set in LSR are still set. The receiver shift register is not cleared. Any

Receive FIFO Service Request Interrupts are cleared.

Note: After the FIFO is cleared, RESETRF is automatically reset to 0.

0 = no effect

1 = The receiver FIFO is cleared (FIFO counter set to 0). After clearing, bit is

automatically reset to 0

00

2

Transmit and Receive FIFO Enable (TRFIFOE): Enables/disables the transmitter

and receiver FIFOs. When TRFIFOE = 1, both FIFOs are enabled (FIFO Mode).

When TRFIFOE = 0, the FIFOs are both disabled (non-FIFO Mode). Writing a 0 to

this bit clears all bytes in both FIFOs. When changing from FIFO mode to non-FIFO

mode and vice versa, data is automatically cleared from the FIFOs. Any FIFO

Service Request Interrupts are cleared when TRFIFOE is cleared.

Note: This bit must be 1 when other bits in this register are written, or the other bits

are not programmed.

0 = FIFOs are disabled

1 = FIFOs are enabled