26 Intel

®

Xeon™ Processor, Intel

®

E7520 Chipset, Intel

®

6300ESB ICH Development Kit User’s Manual

System Overview

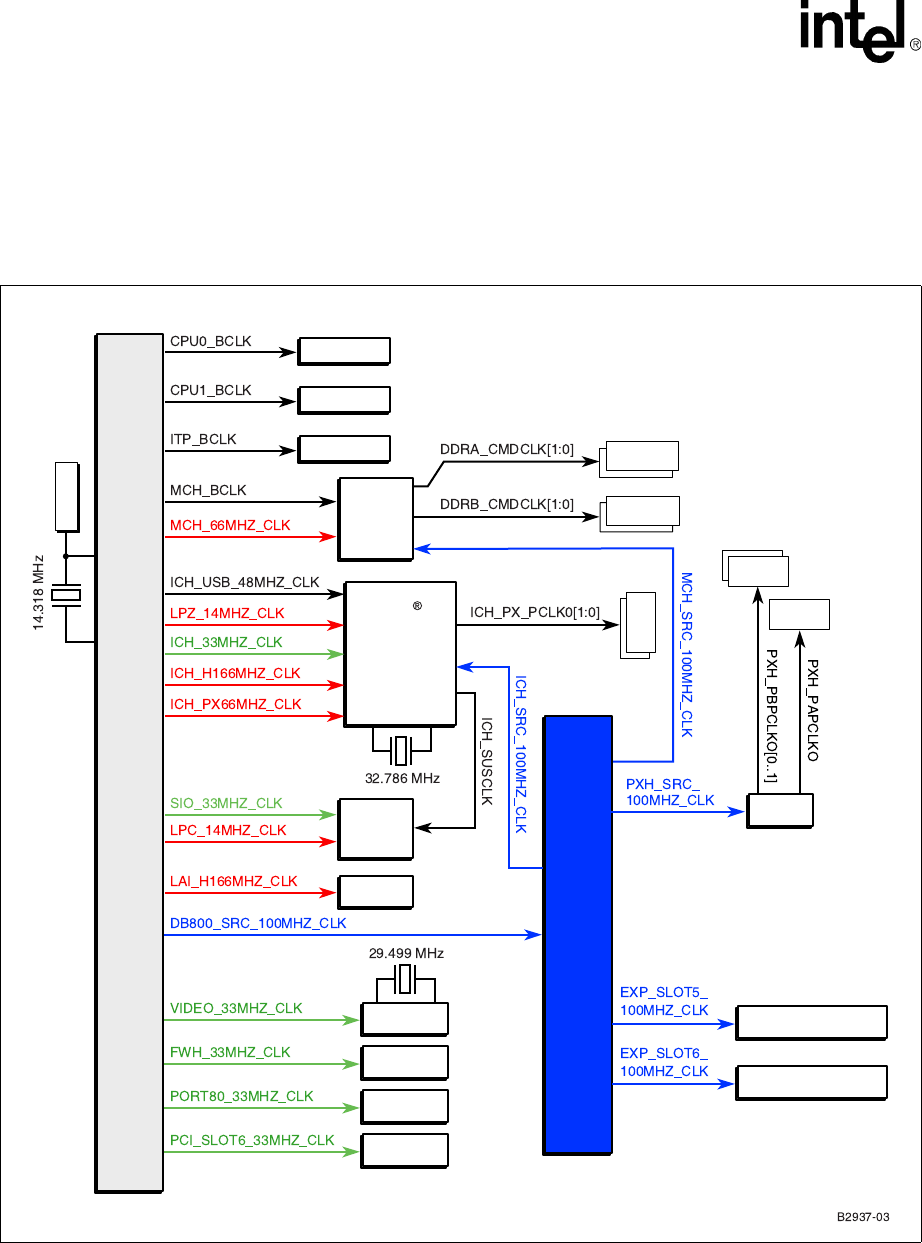

5.2 Platform Clocking

The CRB uses one CK409B Clock Synthesizer to generate the host differential pair clocks and the

100 MHz differential clock to the DB800. The DB800 then generates the 100 MHz differential pair

clock for the PCI Express* devices. Figure 6 shows the CRB clock configuration.

Figure 6. Clock Block Diagram

Intel

6300ESB

I/O

Controller

Hub

MCH

DDRA

CPU0

CPU1

ITP

DDRB

SIO

HI LAI

PXH

Video

FWH

Port 80

PCI Express Slot

PCI Express Slot

PCI 2.2

DB800

PCI-X

PCI-X

PCI-X

CK-409

SMA