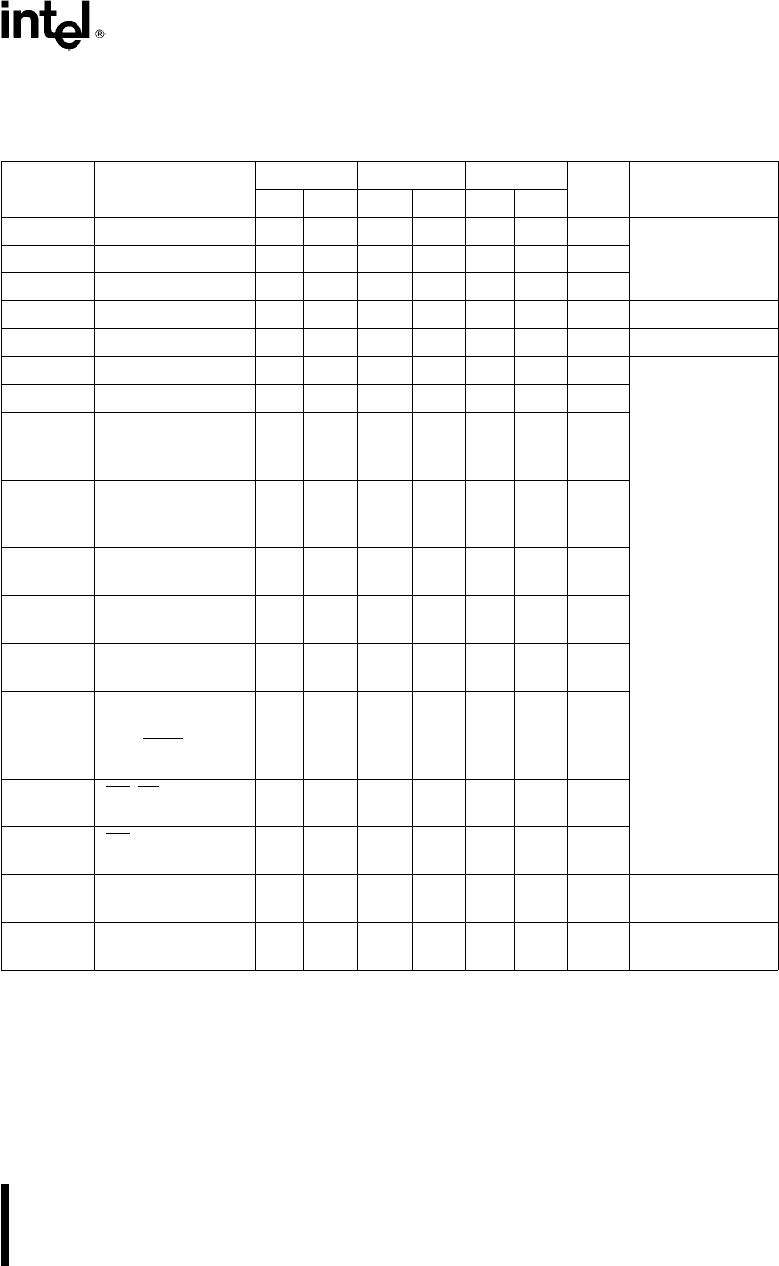

8086

AC CHARACTERISTICS

MAX MODE SYSTEM (USING 8288 BUS CONTROLLER)

TIMING REQUIREMENTS

Symbol Parameter

8086 8086-1 8086-2

Units

Test

Min Max Min Max Min Max

Conditions

TCLCL CLK Cycle Period 200 500 100 500 125 500 ns

TCLCH CLK Low Time 118 53 68 ns

TCHCL CLK High Time 69 39 44 ns

TCH1CH2 CLK Rise Time 10 10 10 ns From10V to 35V

TCL2CL1 CLK Fall Time 10 10 10 ns From35V to 10V

TDVCL Data in Setup Time 30 5 20 ns

TCLDX Data in Hold Time 10 10 10 ns

TR1VCL RDYSetup Time 35 35 35 ns

into 8284A

(Notes 1 2)

TCLR1X RDYHold Time 0 0 0 ns

into 8284A

(Notes 1 2)

TRYHCH READY Setup 118 53 68 ns

Time into 8086

TCHRYX READY Hold Time 30 20 20 ns

into 8086

TRYLCL READY Inactive to

b

8

b

10

b

8ns

CLK (Note 4)

TINVCH Setup Time for 30 15 15 ns

Recognition (INTR

NMI TEST

)

(Note 2)

TGVCH RQGT Setup Time 30 15 15 ns

(Note 5)

TCHGX RQ Hold Time into 40 20 30 ns

8086

TILIH Input Rise Time 20 20 20 ns From 08V to 20V

(Except CLK)

TIHIL Input Fall Time 12 12 12 ns From20V to 08V

(Except CLK)

19