54 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Host Software Interface

• Bits 23:21 - Reserved. These bits are reserved.

• Bit 20 - FC Paused Low. This read only bit is an indication of the device flow control state.

It is set by the device when it receives a pause low command with a value greater than zero and

cleared when the flow control timer reaches zero or a pause frame is received.

• Bit 19 - FC Paused. This read only bit is an indication of the device flow control state. It is

set by the device when it receives a pause command with a value greater than zero and cleared

when the flow control timer reaches zero.

• Bit 18 - FC Full. This read only bit indicates device flow control state. It is set by the device

when it sends a pause command regardless of its cause (either due to the FIFO reaching the

flow control threshold or due to the device fetching an RFD with its FCP bit set or due to

writing into the Xoff bit). The bit is cleared by the device when it exits the above mentioned

state.

• Bit 17 - Xoff. Writing 1 to this bit forces the Xoff request to 1. This causes the device to

behave as if the FIFO extender is full. The Xoff request is cleared by writing 1 to the Xon bit

(bit 16). Reading this bit returns 1 after it was set and 0 after the Xon bit was set. This bit

returns 1 after an Xoff request was generated through the RFD Xoff bit until the Xon bit is set.

• Bit 16 - Xon. Writing 1 to this bit resets the Xoff request to the device. The Xoff request can

become active through the RFD Xoff bit or if the driver writes 1 to the Xoff bit (bit 17).

Reading this bit returns 0.

• Bits 15:11 - Reserved. These bits are reserved.

• Bits 10:8 - FC Threshold. The 82558 or later generation controller is capable of generating a

flow control pause frame when its receive FIFO is almost full. This three-bit field determines

the number of bytes left in the receive FIFO when the pause frame is generated. The trade-off

occurs between a higher degree of data integrity (high flow control threshold value) or high

performance (low flow control threshold value).

6.3.9 Power Management Driver Register

The Power Management Driver Register (PMDR) provides an indication of power management

events. It is an 8-bit field located at offset 18h of the CSR. This register is only present in the 82558

and later generation controllers and is not valid on the 82557.

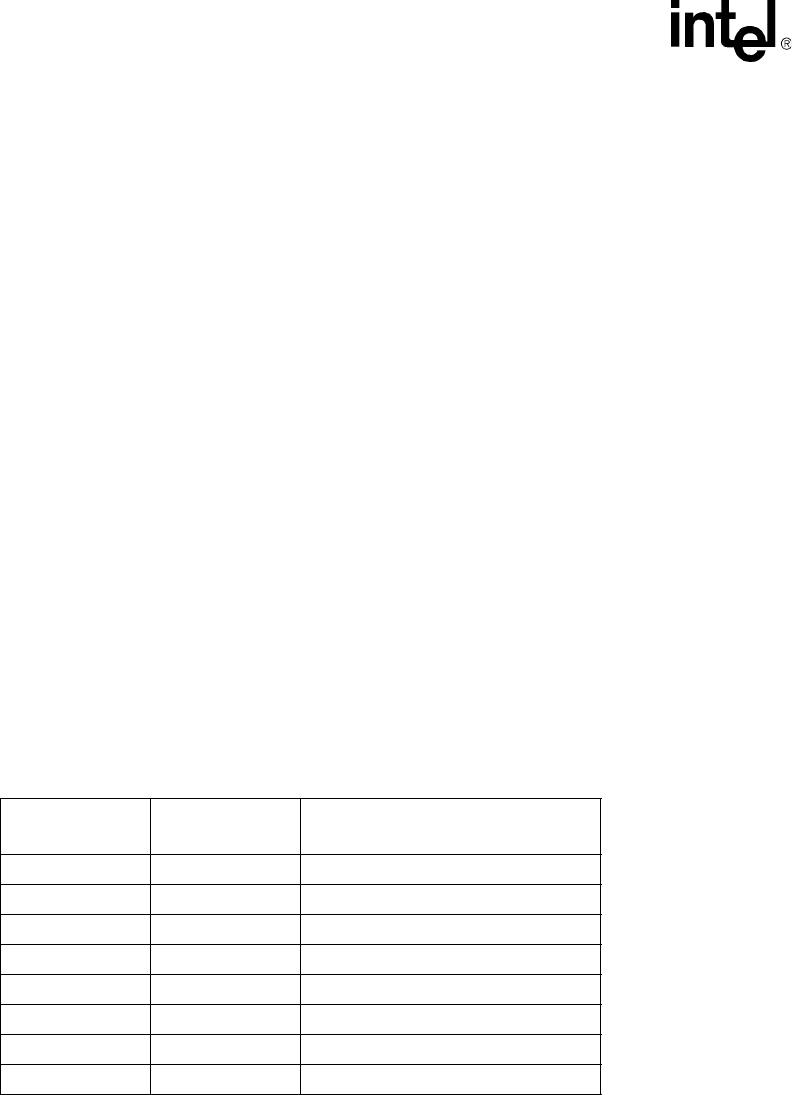

Table 30. Flow Control Threshold Values

FC TH Value

FC TH (free bytes

in receive FIFO)

Comment

000 0.5 Kbyte Fast system (recommended default).

001 1 Kbyte

010 1.25 Kbyte

011 1.5 Kbyte

100 1.75 Kbyte

101 2 Kbyte

110 2.25 Kbyte

111 2.5 Kbyte Slow system.