56 Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual

Host Software Interface

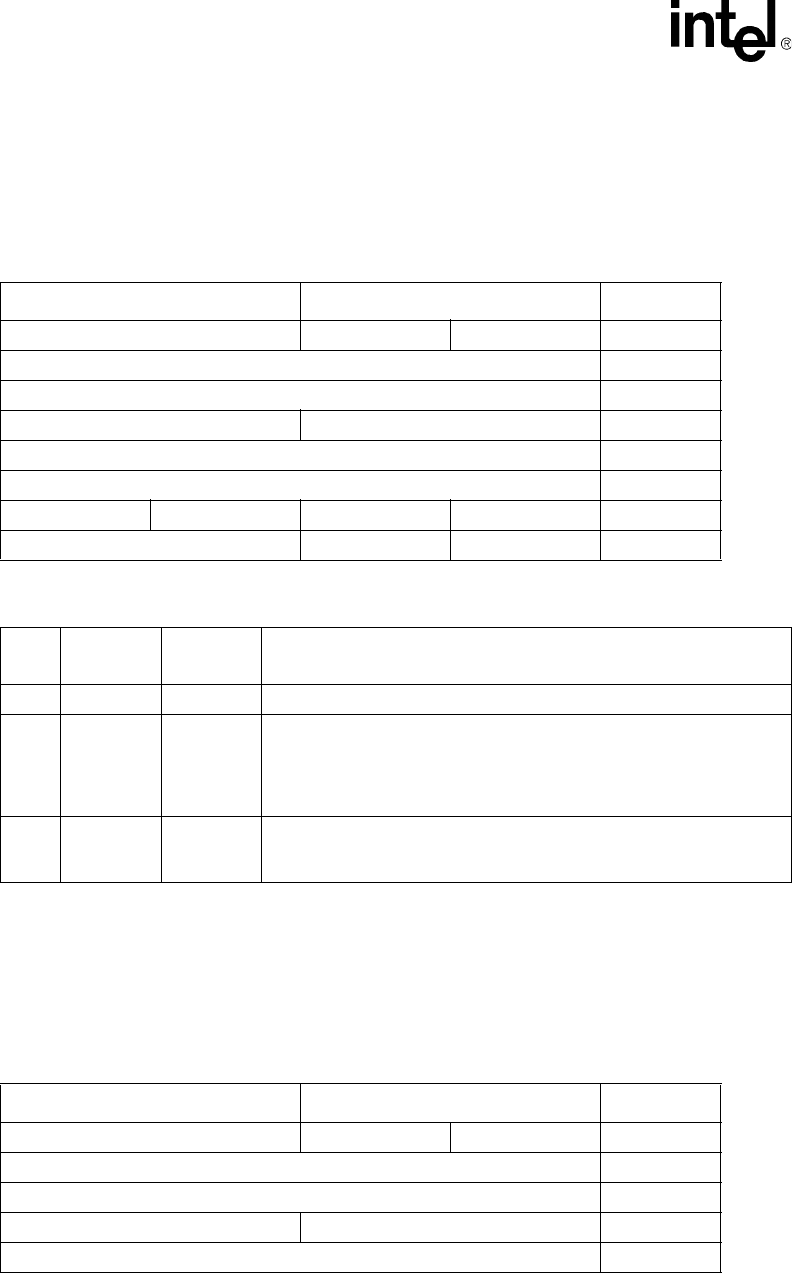

6.3.10 General Control Register

The General Control register provides control over some general purpose features in the 82559. It

is an 8-bit field at offset 1Ch of the CSR. This register is only present in the 82559 and later

generation controllers and is not valid for the 82558 or 82557.

6.3.11 General Status Register

The General Status register provides some basic status information in the 82559. It is an 8-bit entity

at offset 1Dh of the CSR. This register is only present in the 82559 and is not valid for the 82558 or

82557.

Table 33. General Control Register Location

Upper Word (D31:D16) Lower Word (D15:D0) Offset

SCB Command Word SCB Status Word Base + 0h

SCB General Pointer Base + 4h

PORT Base + 8h

EEPROM Control Register Reserved Base + Ch

MDI Control Register Base + 10h

Early Receive Interrupt Receive Byte Count Register Base + 14h

PMDR FC Xon/Xoff FC Threshold Early Rx Int Base + 18h

Reserved General Status General Control Base + 1Ch

Table 34. General Control Register

Bits Operation

Default

PCI Reset

Description

7:2 R 0 Reserved.

1R/W 0

Deep Power Down on Link Down. When this bit is 1, the 82559 may

enter a deep power down state (sub 7 mA) in the D2 and D3 power

states while the link is down. At this state, the 82559 does not maintain

link integrity. It is not supported for point to point connection of two end

stations.

0R/W 0

Clockrun Disable. When this bit is 1, the 82559 always requests the PCI

CLK. This mode can be used to overcome potential receive overruns

caused by a very long system CLKRUN latency.

Table 35. General Status Register Location

Upper Word (D31:D16) Lower Word (D15:D0) Offset

SCB Command Word SCB Status Word Base + 0h

SCB General Pointer Base + 4h

PORT Base + 8h

EEPROM Control Register Reserved Base + Ch

MDI Control Register Base + 10h