Technical Reference

71

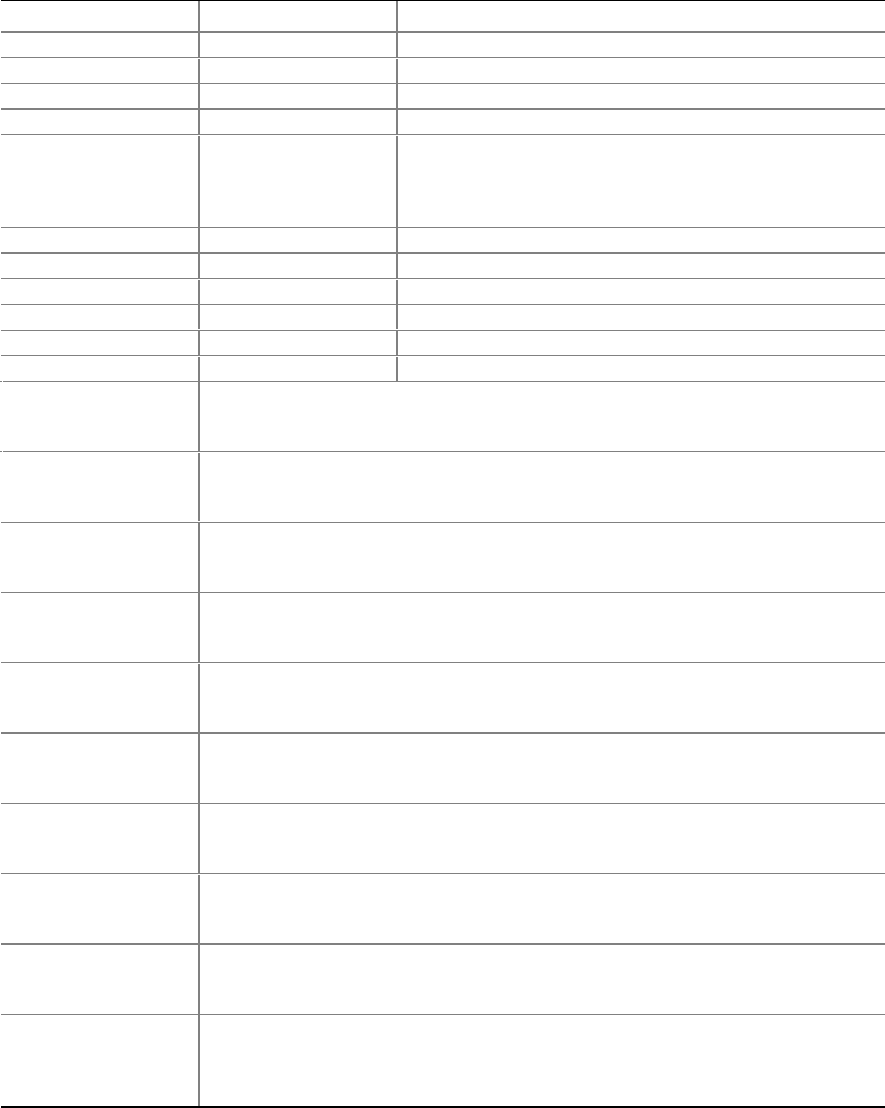

Table 29. I/O Map (continued)

Address (hex) Size Description

03F0 - 03F5 6 bytes Diskette channel 1

03F6 1 byte Primary IDE channel command port

03F8 - 03FF 8 bytes COM1

04D0 - 04D1 2 bytes Edge / level triggered PIC

One of these ranges:

0530 - 0537

0E80 - 0E87

0F40 - 0F47

8 bytes Windows Sound System

LPTn + 400h 8 bytes ECP port, LPTn base address + 400h

0CF8 - 0CFB** 4 bytes PCI configuration address register

0CF9*** 1 byte Turbo and reset control register

0CFC - 0CFF 4 bytes PCI configuration data register

FFA0 - FFA7 8 bytes Primary bus master IDE registers

FFA8 - FFAF 8 bytes Secondary bus master IDE registers

96 contiguous bytes

starting on a 128-byte

divisible boundary

ICH (ACPI + TCO)

64 contiguous bytes

starting on a 64-byte

divisible boundary

D815EEA desktop board resource

64 contiguous bytes

starting on a 64-byte

divisible boundary

Onboard audio controller

32 contiguous bytes

starting on a 32-byte

divisible boundary

ICH2 (USB#1)

32 contiguous bytes

starting on a 32-byte

divisible boundary

ICH2 (USB#2)

16 contiguous bytes

starting on a 16-byte

divisible boundary

ICH2 (SMBus)

64 contiguous bytes

starting on a 64-byte

divisible boundary

ICH2 modem controller

32 contiguous bytes

starting on a 32-byte

divisible boundary

ICH2 audio mixer

64 contiguous bytes

starting on a 64-byte

divisible boundary

ICH2 LAN controller

4096 contiguous bytes

starting on a

4096-byte divisible

boundary

Intel 82801BA PCI bridge

* Default, but can be changed to another address range.

** Dword access only.

*** Byte access only.