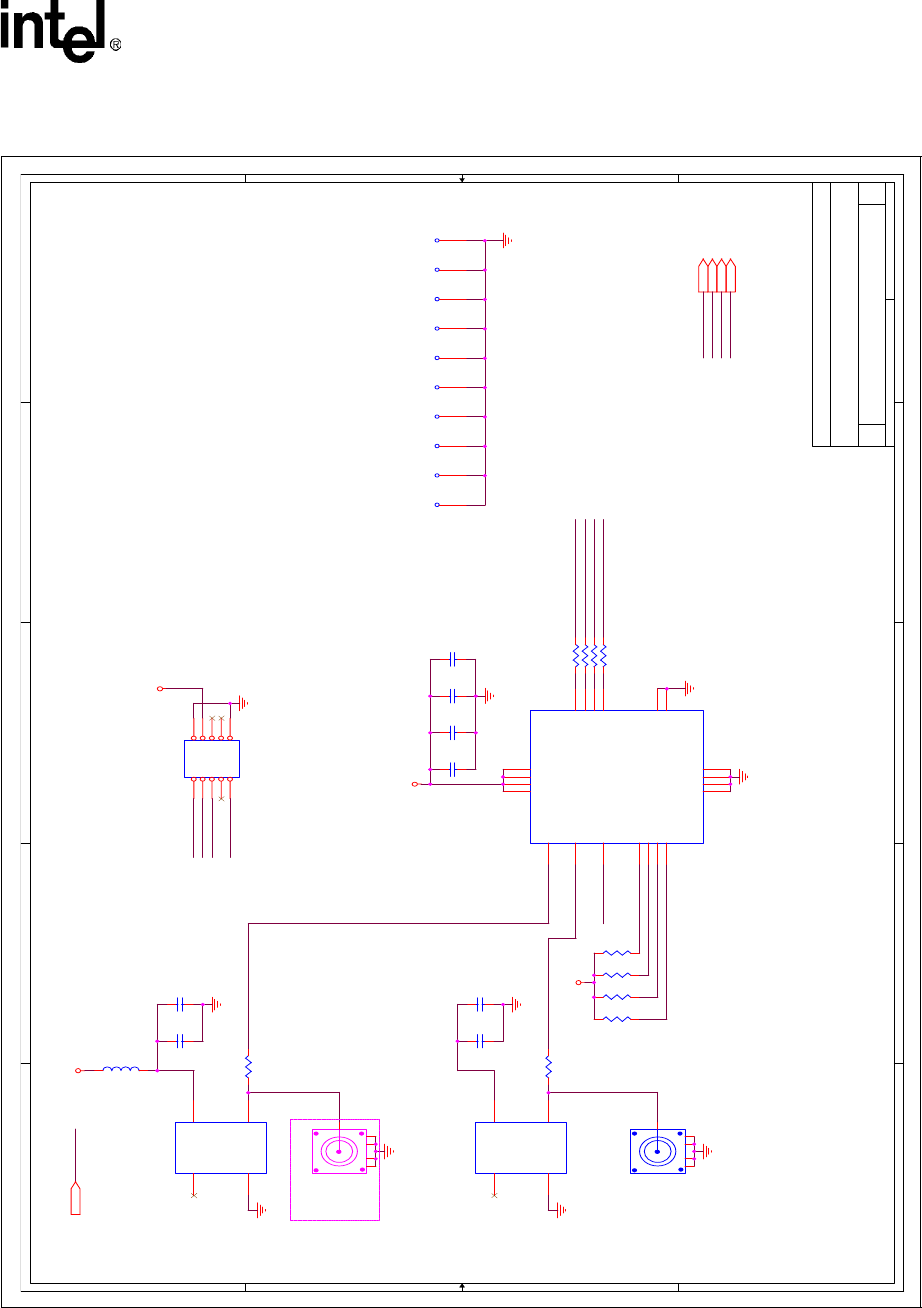

LXD9785 PQFP Demo Board with FPGA for SS-SMII (Fiber)-to-MII Conversion

Development Kit Manual 31

Document #: 249323

Revision #: 003

Rev. Date: January 24, 2002

Figure 16. Clock Distribution

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

DISTRIBUTE

**NOTE** DURING LAYOUT THESE

NETS MUST HAVE CONTROLLED

IMPEDANCES OF 50 OHMS

CLOCK DISTRIBUTION A2

LXD9785 SS/SMII MII FX DV BOARD

B

14 18Wednesday, February 21, 2001

Title

Size Document Number Rev

Date: Sheet

of

VCCX

SECTION

PLD2_TDI

REF_CLK_0

REF_CLK_2

REF_CLK_1

REF_CLK_3

SECTION

REF_CLK_1

REF_CLK_3

REF_CLK_2

REF_CLK_0

PLD2_TMS

PLD2_TMS

PLD2_TDO

PLD2_TCK

PLD2_TDI

PLD2_TCK

PLD2_TDO

VCCX

SECTION3

REF_CLK_1 3

REF_CLK_3 13

REF_CLK_2 13

REF_CLK_0 3

GND

VCC_EXT

GND

GND

GND

GND

GND

VCC_EXT

VCC_EXT

VCC_EXT

GND

GND

GND

GND

GND

TP70

1

TP71

1

TP68

1

C156

0.1uF

C157

0.01uF

Y1

125 MHzCRYSTAL OSC

1

7 8

14

NC

GND OUT

VCC

R454

50 1%

FB8

Ferrite Bead

C349

0.1uF

C348

0.01uF

C346

0.01uF

C347

0.1uF

R736

1K

J5

SMA(5 PIN)

R735

1K

J4

SMA(5 PIN)

R734

1K

R733

1K

R455 50 1%

R456 50 1%

R460 50 1%

TP62

1

R461 50 1%

TP63

1

JP14

HEADER 5X2

12

34

56

78

910

TP64

1

C350

0.1uF

TP69

1

C351

0.01uF

TP65

1

Y2

125 MHzCRYSTAL OSC

1

7 8

14

NC

GND OUT

VCC

TP66

1

R732

50 1%

TP67

1

U46

EPM7032AETC44-4_CLK_DISTR

1

4

7

9

17

18

20

24

26

29

32

36

37

38

39

40

41

42

16

15

19

TDI

GNDIO

TMS

VCCIO

VCCINT

CLK_OUT1

CLK_OUT3

GNDIO

TCK

VCCIO

TDO

GNDINT

CLK1

INPUT1

INPUT2

CLK2

VCCINT

SECTION

GNDINT

CLK_OUT0

CLK_OUT2