Memory and I/O Map

Reference – 36 EPM-4 Reference Manual

Memory and I/O Map

ÉLANSC520 MEMORY MAPPED CONFIGURATION REGION (MMCR) REGISTERS

Much of the functionality incorporated into the ÉlanSC520 Microcontroller, such as the

watchdog timer, CPU speed control, and general-purpose timer, can be controlled and monitored

through the Memory Mapped Configuration Region (MMCR) registers. The MMCR registers

occupy 4KB of memory space. For convenience, these registers are made available at boot time in

the first megabyte of system RAM, at DF000h.

Wherever the MMCR is located, its 4KB footprint will cover and take precedence over the

underlying memory space function. For example, when the D0000h page function is set to ISA

bus, DF000h through DFFFFh will instead by occupied by the MMCR. For this reason, the

maximum BIOS extension size is reduced from 64KB to 60KB.

In the event of an address conflict, the MMCR base address can be moved at any time with an I/O

write to the Configuration Base Address Register (CBAR), located at I/O address FFFCh. Refer

to the ÉlanSC520 Register Set Manual for further details.

M

EMORY MAP

The lower 1 MB memory map of the EPM-4 is arranged as shown in the following table.

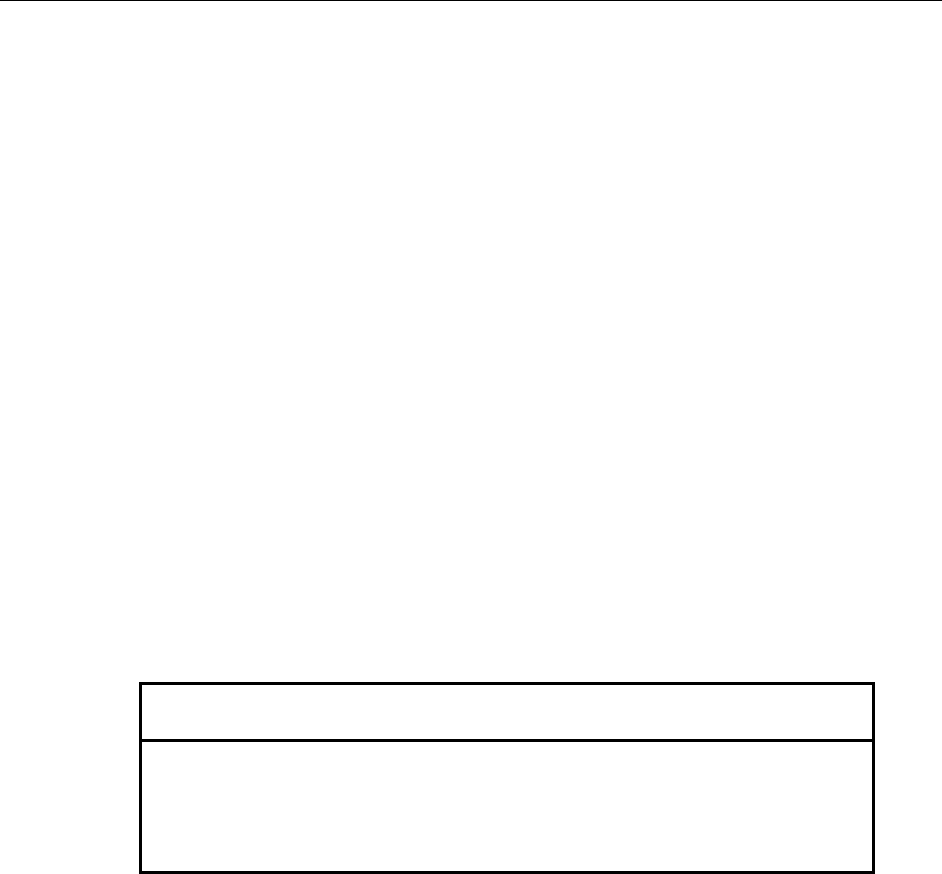

Table 8: Memory Map

Start

Address

End

Address

Comment

E0000h FFFFFh System BIOS

DF000h DFFFFh MMCR Registers (see note)

D0000h DEFFFh ISA memory, BIOS extension, or RAM

C0000h CFFFFh Reserved for Video BIOS

A0000h BFFFFh Reserved for Video RAM

00000h 9FFFFh System DRAM

Note: Default location. If MMCR is relocated, this memory space is allocated to ISA

memory, BIOS extension, or RAM, depending on how the D0000h page function

is set in CMOS Setup.