AT INTERFACE DESCRIPTION

5 – 4

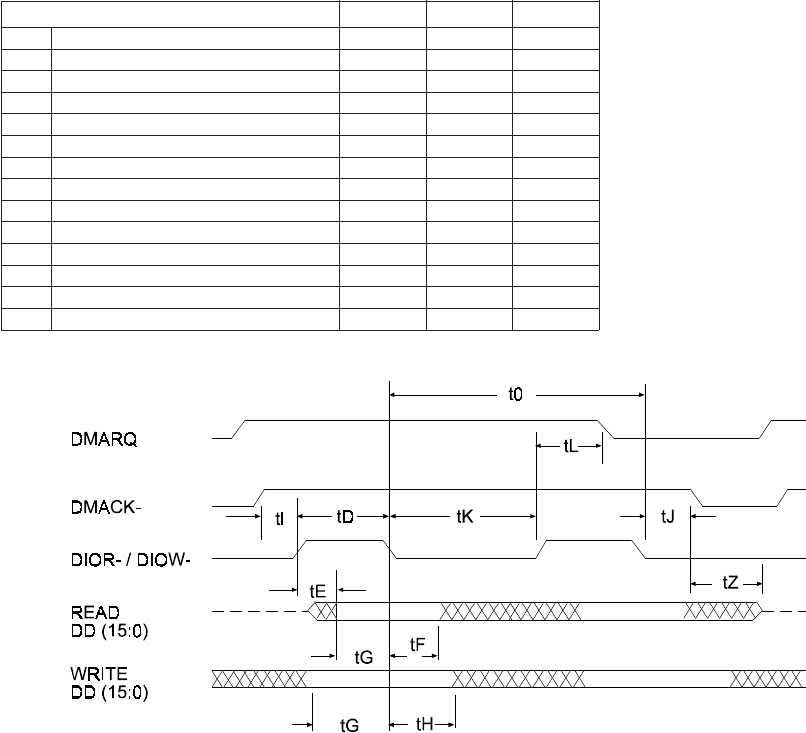

DMA Timing

SRETEMARAPGNIMIT0EDOM1EDOM2EDOM

0temiTelcyC

)nim(

sn084sn051sn021

CtyaledQRAMDotKCAMD

Dt-WOID/-ROID

)nim(

sn512sn08sn07

Etsseccaatad-ROID

)nim(

sn051sn06

Ftdlohatad-ROID

)nim(

sn5sn5sn5

Gtputesatad-WOID/-ROID

)nim(

sn001sn03sn02

Htdlohatad-WOID

)nim(

sn02sn51sn01

Itputes-WOID/-ROIDotKCAMD

)nim(

000

JtdlohKCAMDot-WOID/-ROID

)nim(

sn02sn5sn5

rKthtdiweslupdetagen-ROID

)nim(

sn05sn05sn52

wKthtdiweslupdetagen-WOID

)nim(

sn512sn05sn52

rLtyaledQRAMDot-ROID

)xam(

sn021sn04sn53

wLtyaledQRAMDot-WOID

)xam(

sn04sn04sn53

Ztetatsirtot-KCAMD

)xam(

sn02sn52sn52

Figure 5 - 3

Multi-word DMA Data Transfer