AT INTERFACE DESCRIPTION

5 – 5

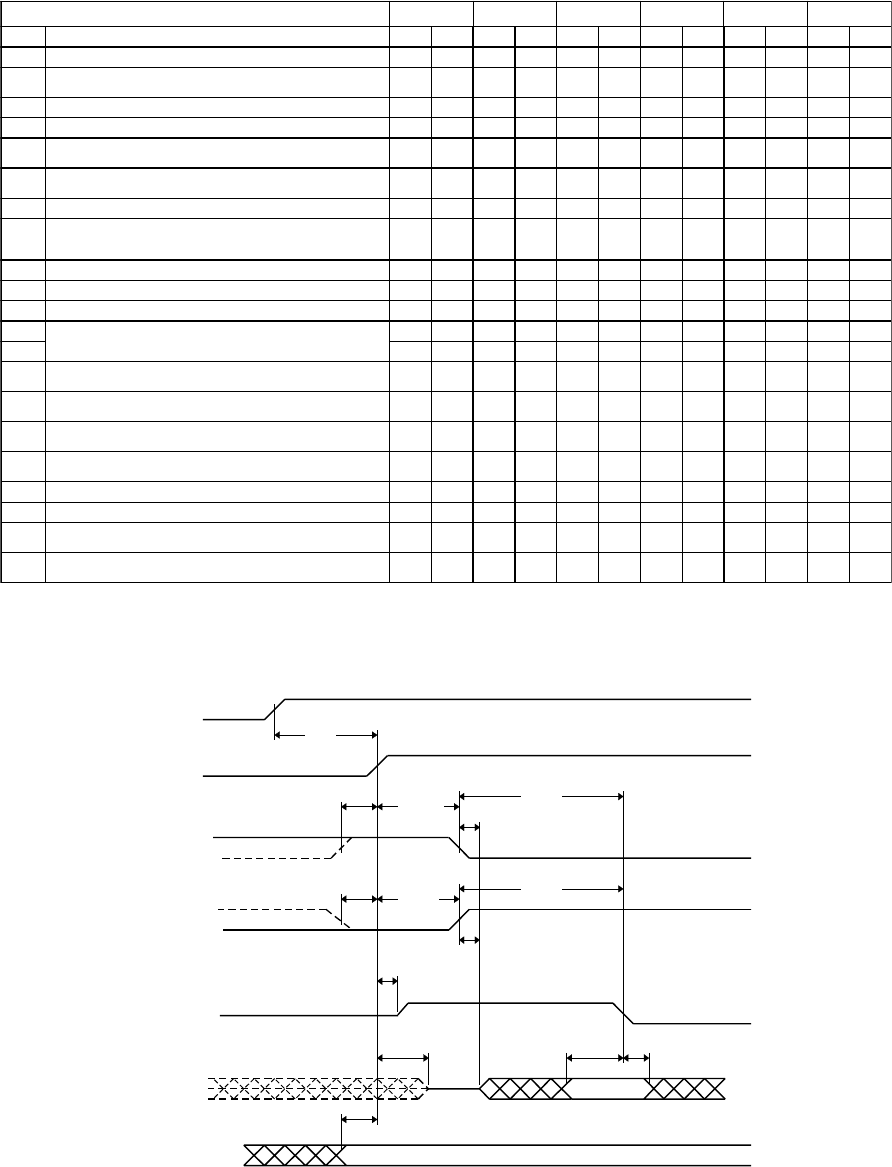

Ultra DMA TimingUltra DMA Timing

Ultra DMA TimingUltra DMA Timing

Ultra DMA Timing

TIMING PARAMETERS

(all times in nanoseconds)

MODE 0 MODE 1 MODE 2 MODE 3 MODE 4 MODE 5

MIN MAX MIN MAX MIN MAX MIN MAX MIN MAX MIN MAX

t

CYC

C

y

cle Time (from STROBE ed

g

e to STROBE ed

g

e) 112 73 54 39 25 16.8

t2

CYC

Two c

y

cle time (from risin

g

ed

g

e to next risin

g

ed

g

e or

from fallin

g

ed

g

e to next fallin

g

ed

g

e of STROBE)

230 153 115 86 57 38

t

DS

Data setup time (at recipient) 15 10 7 7 5 4

t

DH

Data hold time (at recipient) 5 5 5 5 5 4.6

t

DVS

Data valid setup time at sender (time from data bus bein

g

valid until STROBE ed

g

e)

70 48 31 20 6.7 4.8

t

DVH

Data valid hold time at sender (time from STROBE ed

g

e

until data ma

y

g

o invalid)

6.2 6.2 6.2 6.2 6.2 4.8

t

FS

First STROBE (time for device to send first STROBE) 0 230 0 200 0 170 0 130 0 120 0 90

t

LI

Limited interlock time (time allowed between an action b

y

one a

g

ent, either host or device, and the followin

g

action

b

y

the other a

g

ent)

0 150 0 150 0 150 0 100 0 100 0 75

t

ML I

Interlock time with minimum 20 20 20 20 20 20

t

UI

Unlimited interlock time 000000

t

AZ

Maximum time allowed for outputs to release 10 10 10 10 10 10

t

ZAH

Minimum dela

y

time required for output drivers turnin

g

on

(from released state)

20 20 20 20 20 20

t

ZAD

000000

t

ENV

Envelope time (all control si

g

nal transitions are within the

DMACK envelope b

y

this much time)

20 70 20 70 20 70 20 55 20 55 20 50

t

SR

STROBE to DMARDY (response time to ensure the

s

y

nchronous pause case when the recipient is pausin

g

)

50 30 20 NA NA NA

t

RFS

Read

y

-to-final-STROBE time (no more STROBE ed

g

es

ma

y

be sent this lon

g

after receivin

g

DMARDY- ne

g

ation)

75 70 60 60 60 50

t

RP

Read

y

-to-pause time (time until a recipient ma

y

assume

that the sender has paused after ne

g

ation of DMARDY-)

160 125 100 100 100 85

t

IORDYZ

Pull-up time before allowin

g

IORDY to be released 20 20 20 20 20 20

t

ZIORDY

Minimum time device shall wait before drivin

g

IORDY000000

t

ACK

Setup and hold times before assertion and ne

g

ation of

DMACK-

20 20 20 20 20 20

t

SS

Time from STROBE ed

g

e to STOP assertion when the

sender is stoppin

g

50 50 50 50 50 50

DMARQ

(device)

DMACK-

(host)

STOP

(host)

HDMARDY-

(host)

DSTROBE

(device)

DD(15:0)

t

ZAD

DA0, DA1, DA2,

CS0-, CS1-

t

UI

t

ZAD

t

ACK

t

ACK

t

ENV

t

ENV

t

ZIORDY

t

FS

t

FS

t

VDS

t

AZ

t

DVH

t

ACK

Figure 5 - 4

Initiating an Ultra DMA Data In Burst