536

CHAPTER 23 EXTERNAL DEVICE EXPANSION FUNCTION

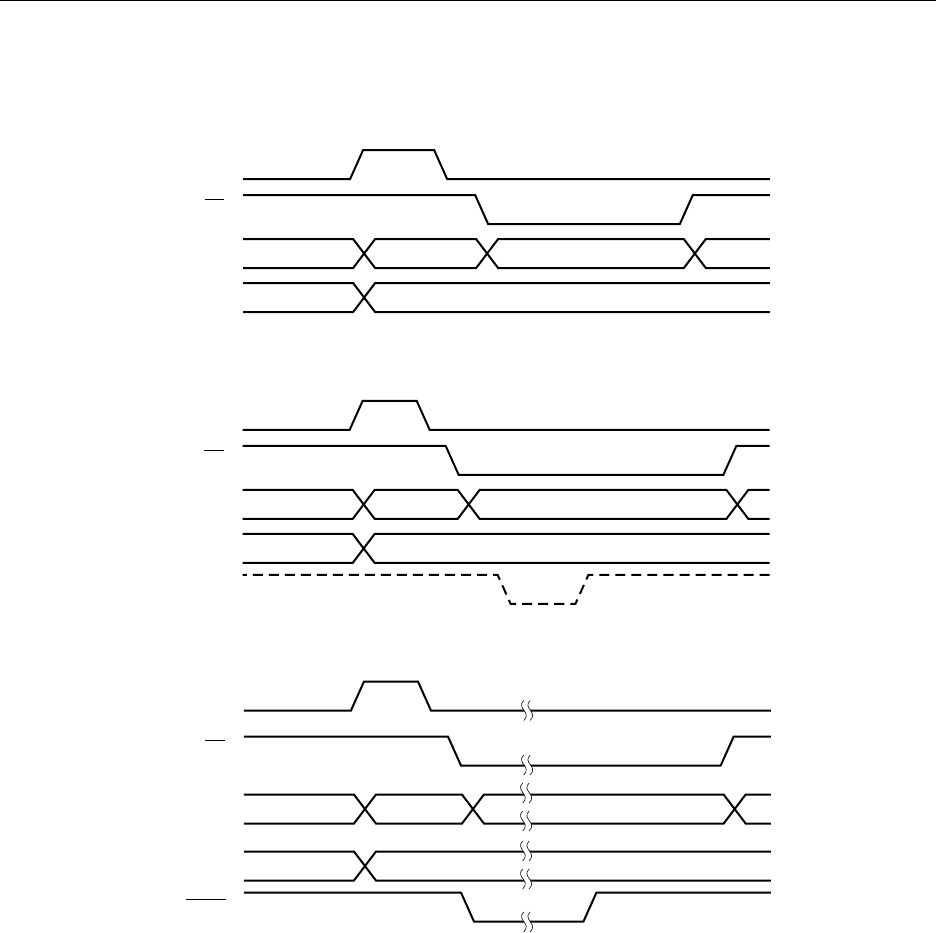

Figure 23-6. External Memory Read Timing in Multiplexed Bus Mode

(a) No wait (PW1, PW0 = 0, 0) setting

(b) Wait (PW1, PW0 = 0, 1) setting

(c) External wait (PW1, PW0 = 1, 1) setting

Higher Address

ASTB

RD

AD0 to AD7

A8 to A15

Lower Address

Read Data

ASTB

RD

AD0 to AD7

A8 to A15

Lower Address

Read Data

Higher Address

Internal Wait Signal

(1-clock wait)

ASTB

RD

Lower Address

Read DataAD0 to AD7

A8 to A15

Higher Address

WAIT