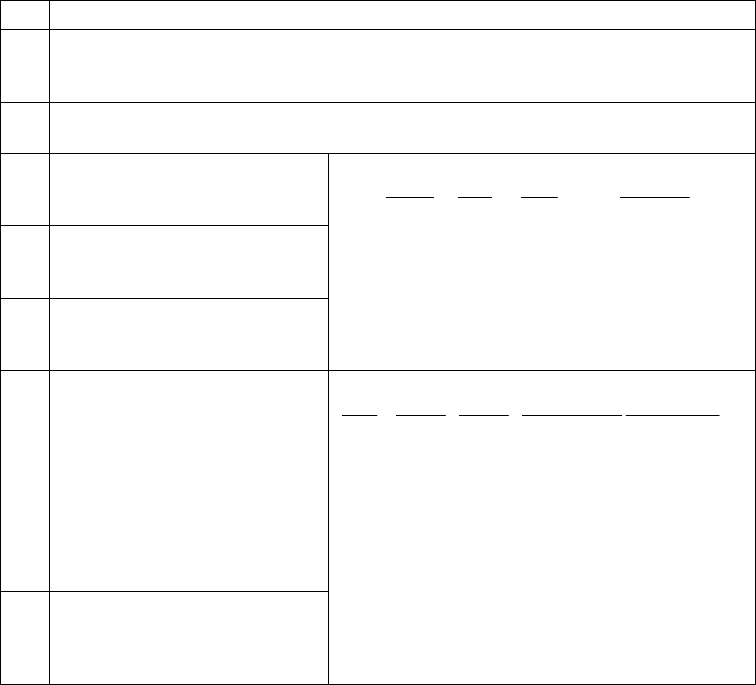

LINE CONTROL REGISTER

This register is located at I/O address [base+3]. It is used for specifying

the format of the asynchronous serial data to be processed by the UART, and to

set the Divisor Latch Access Bit (DLAB) allowing access to the baud rate divisor

latches.

WLS0 ---

0

Word length select:

Determines the number

of bits per transmitted

word.

WLS1 ---

1

STB

WLS1 WLS0 WORD LEN STOP BITS

0 0 0 5 bits 1

0 0 1 6 bits 1

0 1 0 7 bits 1

0 1 1 8 bits 1

1 0 0 5 bits 1.5

1 0 1 6 bits 2

1 1 0 7 bits 2

1 1 1 8 bits 2

STB --- Number of stop bits:

Sets the number of stop bits

transmitted.

2

PEN --- Parity enable:

Enables parity on transmission and

verification on reception.

3

EPS --- Even parity select:

Selects even or odd parity if parity is

enabled.

4

STKP

EPS PEN PARITY

x x 0 None

0 0 1 Odd

0 1 1 Even

1 0 1 Logic 1

1 1 1 Logic 0

STKP --- Stick parity:

Forces parity to logic 1 or logic 0 if

parity is enabled.

5

BKCN --- Break control:

When set (logic 1), the serial output (SOUT) is forced to the spacing state (logic 0).

6

DLAB --- Divisor latch access bit:

DLAB must be set to logic 1 to access the baud rate divisor latches. DLAB must be set to logic

0 to access the receiver buffer, transmitting holding register and interrupt enable register.

7

DESCRIPTIONBIT

Figure 18 --- Line Control Register bit definitions

Quatech ES-100D User's Manual 17