( 54 / 72 )

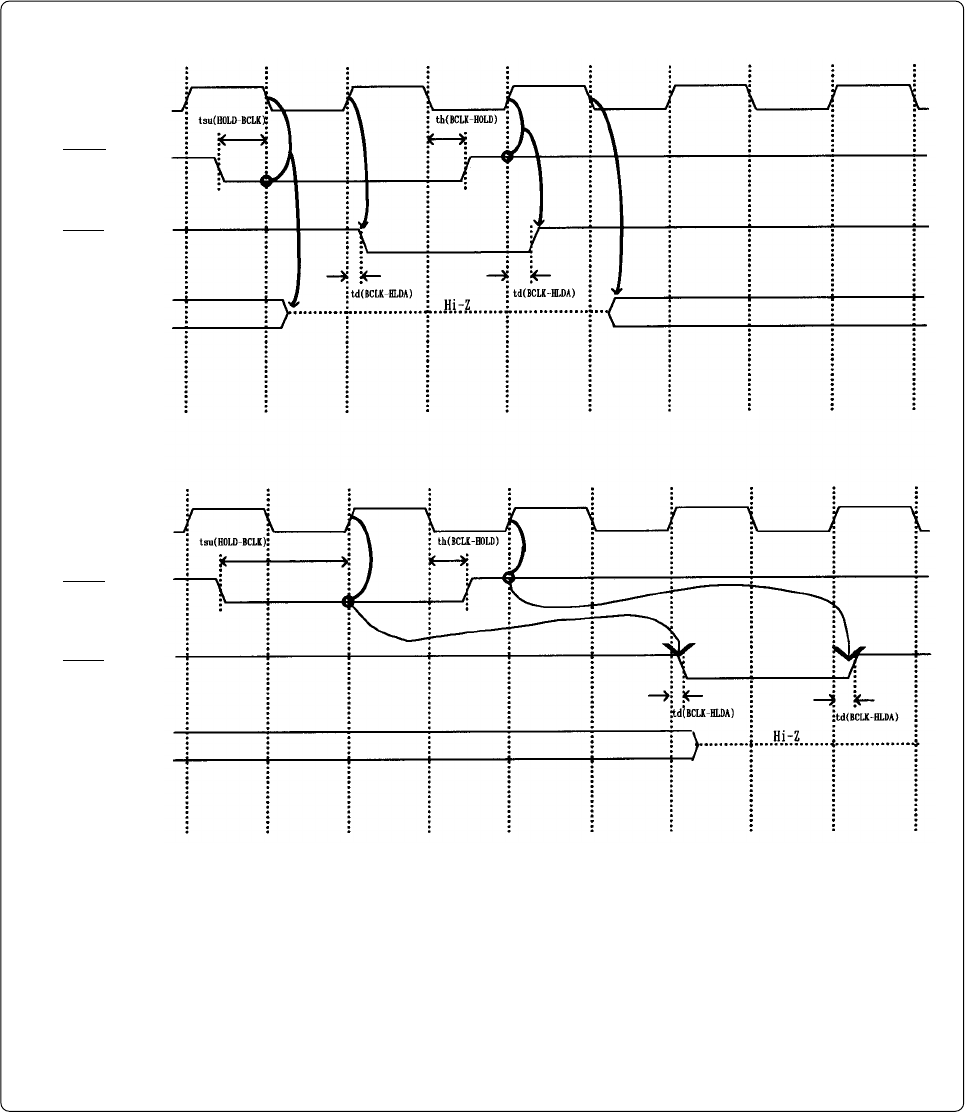

Figure 5.5 Timing requirements

Common to "with wait" and "no-wait" (actual MCU)

BCLK

Common to "with wait" and "no-wait" (this product)

BCLK

Note 1. P00 to P52 will be high-impedance regardless of the input level of BYTE pin and ports P40 to P43 function

selection bit (PM06) of the processor mode register 0.

Note 2. This product will be high-impedance delaying by 2.5 cycles than the actual MCU.

Note 3. The setup time of HOLD is defined by the startup of BCLK, differently from that of actual MCUs.

Conditions:

• V

CC=5V

• Input timing voltage: VIL=1.0V, VIH=4.0V

• Output timing voltage: VOL=2.5V, VOH=2.5V

P0, P1, P2,

P3, P4,

P50 to P52

HOLD input

P0, P1, P2,

P3, P4,

P50 to P52

HLDA output

HOLD input

HLDA output