SH7145F

Asynchronous Serial Data Transmission/Reception

REJ06B0357-0100O/Rev.1.00 March 2004 Page 10 of 17

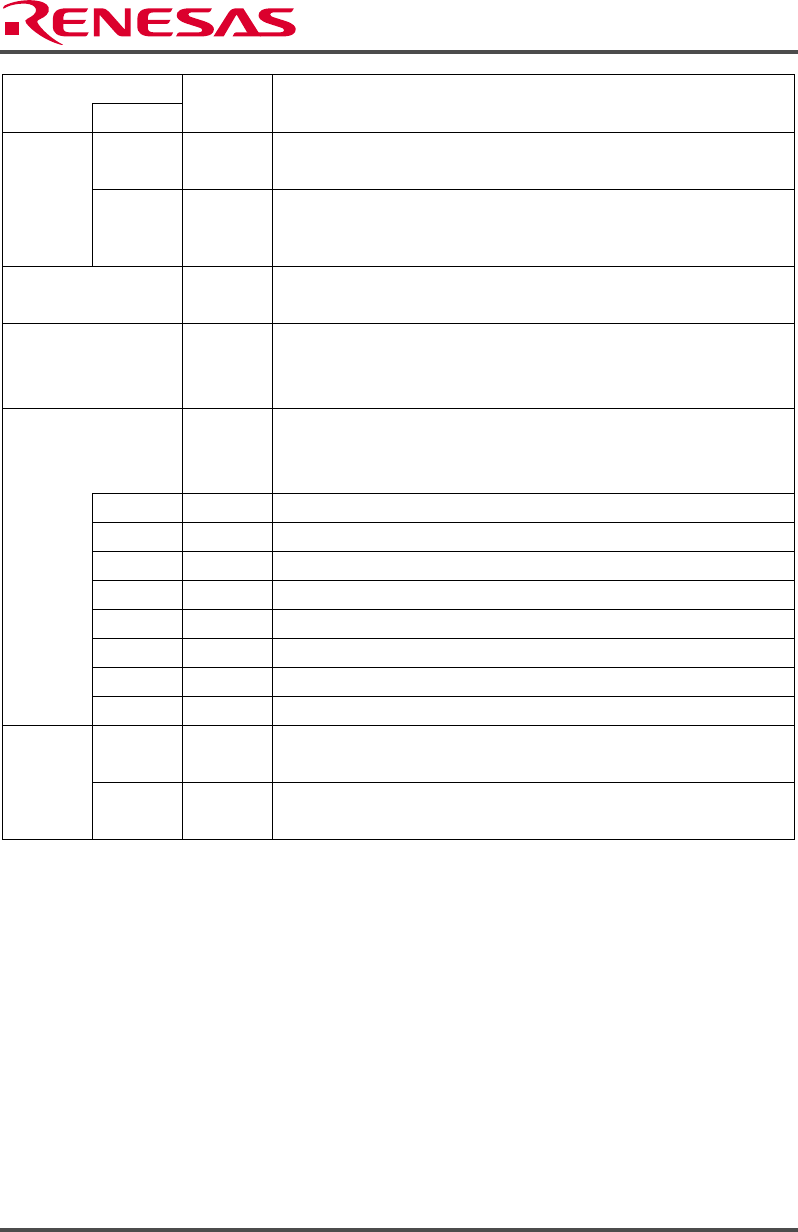

Register

Bit

Set Value Function

SMR_1 MP 0 Multiprocessor mode (enabled in asynchronous mode only)

Multiprocessor communication disabled when 0

CKS1

CKS2

0

0

Clock select 1, 0

When value is 00, Pφ clock selected using on-chip baud rate generator

as clock source

BRR_1 H'40 Bit rate register 1

8-bit register for adjusting bit rate

SDCR_1 H'F2 Serial direction control register 1

DIR bit (bit 3) selects LSB-first or MSB-first

In task example, DIR = 0 (LSB-first)

SSR_1 H'xx Serial status register 1

Comprises SCI1 status flag and transmit and receive multiprocessor bits

Only 0 may be written to the status flag, to clear it

TDRE * Transmit data register empty (status flag)

RDRF * Receive data register full (status flag)

ORER * Overrun error (status flag)

FER * Framing error (status flag)

PER * Parity error (status flag)

TEND * Transmit end (status flag)

MPB 0 Multiprocessor bit

MPBT 0 Multiprocessor bit transfer

PA4MD1

PA4MD0

0

1

Port A control register L2

Function setting for port A multiplex pin (TXD1)

PACRL2

PA3MD1

PA3MD0

0

1

Port A control register L2

Function setting for port A multiplex pin (RXD1)

*: Can only be cleared to 0. Setting to 1 is performed by hardware.