MII/RMII 10/100 Ethernet Transceiver with HP Auto-MDIX and flexPWR

®

Technology in a Small Footprint

Datasheet

SMSC LAN8710/LAN8710i 33 Revision 1.0 (04-15-09)

DATASHEET

4.12 PHY Address Strapping

The PHY ADDRESS bits are latched into an internal register at the end of a hardware reset. The 3-

bit address word[2:0] is input on the PHYAD[2:0] pins. The default setting is 3'b000 as described in

Section 5.3.9.1.

4.13 Variable Voltage I/O

The Digital I/O pins on the LAN8710/LAN8710i are variable voltage to take advantage of low power

savings from shrinking technologies. These pins can operate from a low I/O voltage of +1.8V-10% up

to +3.3V+10%. The I/O voltage the System Designer applies on VDDIO needs to maintain its value

with a tolerance of ± 10%. Varying the voltage up or down, after the transceiver has completed power-

on reset can cause errors in the transceiver operation.

4.14 Transceiver Management Control

The Management Control module includes 3 blocks:

Serial Management Interface (SMI)

Management Registers Set

Interrupt

4.14.1 Serial Management Interface (SMI)

The Serial Management Interface is used to control the LAN8710/LAN8710i and obtain its status. This

interface supports registers 0 through 6 as required by Clause 22 of the 802.3 standard, as well as

“vendor-specific” registers 16 to 31 allowed by the specification. Non-supported registers (7 to 15) will

be read as hexadecimal “FFFF”.

At the system level there are 2 signals, MDIO and MDC where MDIO is bi-directional open-drain and

MDC is the clock.

A special feature (enabled by register 17 bit 3) forces the transceiver to disregard the PHY-Address in

the SMI packet causing the transceiver to respond to any address. This feature is useful in multi-PHY

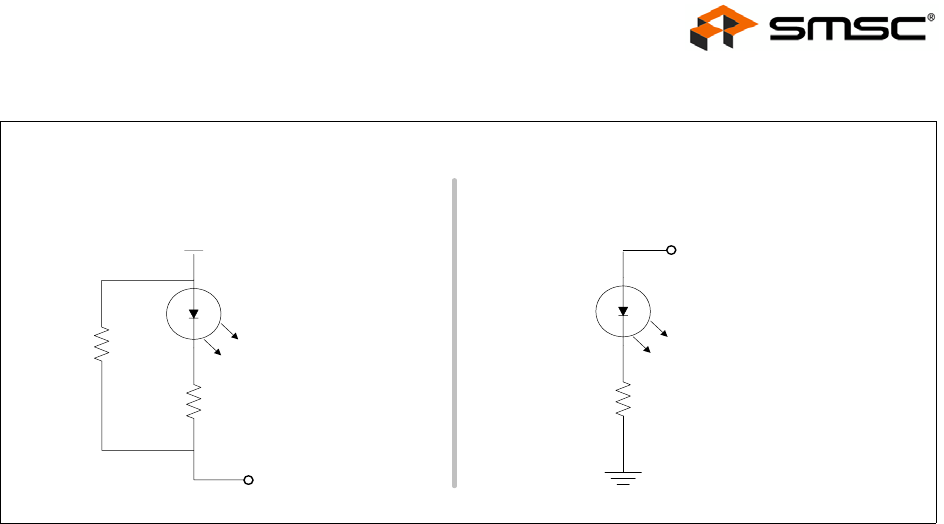

Figure 4.6 REGOFF Configuration on LED1

LED1/REGOFF

~270 ohms

REGOFF = 0

LED output = active high

~270 ohms

VDD2A

REGOFF = 1 (Regulator OFF)

LED output = active low

LED1/REGOFF

10K