Hi-Speed USB 2.0 to 10/100 Ethernet Controller

Datasheet

Revision 1.7 (10-02-08) 6 SMSC LAN9500/LAN9500i

DATASHEET

Chapter 1 Introduction

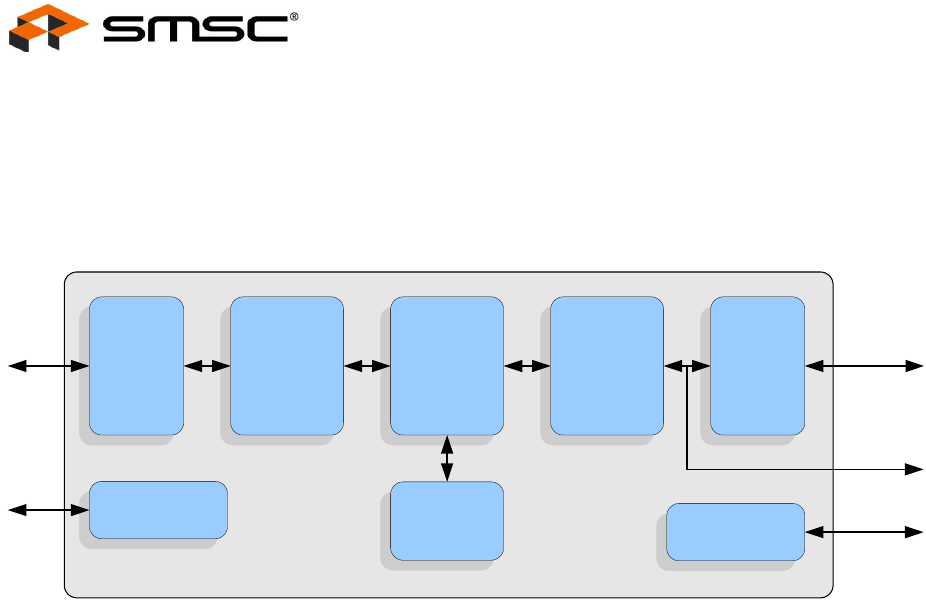

1.1 Block Diagram

1.1.1 Overview

The LAN9500/LAN9500i is a high performance Hi-Speed USB 2.0 to 10/100 Ethernet controller. With

applications ranging from embedded systems, set-top boxes, and PVR’s, to USB port replicators, USB

to Ethernet dongles, and test instrumentation, the LAN9500/LAN9500i is a high performance and cost

competitive USB to Ethernet connectivity solution.

The LAN9500/LAN9500i contains an integrated 10/100 Ethernet PHY, USB PHY, Hi-Speed USB 2.0

device controller, 10/100 Ethernet MAC, TAP controller, EEPROM controller, and a FIFO controller with

a total of 30 KB of internal packet buffering.

The internal USB 2.0 device controller and USB PHY are compliant with the USB 2.0 Hi-Speed

standard. The LAN9500/LAN9500i implements Control, Interrupt, Bulk-in, and Bulk-out USB Endpoints.

The Ethernet controller supports auto-negotiation, auto-polarity correction, HP Auto-MDIX, and is

compliant with the IEEE 802.3 and IEEE 802.3u standards. An external MII interface provides support

for an external Fast Ethernet PHY, HomePNA, and HomePlug functionality.

Multiple power management features are provided, including various low power modes and "Magic

Packet", "Wake On LAN", and "Link Status Change" wake events. These wake events can be

programmed to initiate a USB remote wakeup.

An internal EEPROM controller exists to load various USB configuration information and the device

MAC address. The integrated IEEE 1149.1 compliant TAP controller provides boundary scan via JTAG.

Figure 1.1 LAN9500/LAN9500i System Diagram

TAP

Controller

EEPROM

Controller

USB 2.0

Device

Controller

SRAM

Ethernet

PHY

10/100

Ethernet

MAC

FIFO

Controller

USB

PHY

LAN9500/LAN9500i

MII: To optional

external PHY

Ethernet

EEPROM

JTAG

USB