Timer Registers

www.ti.com

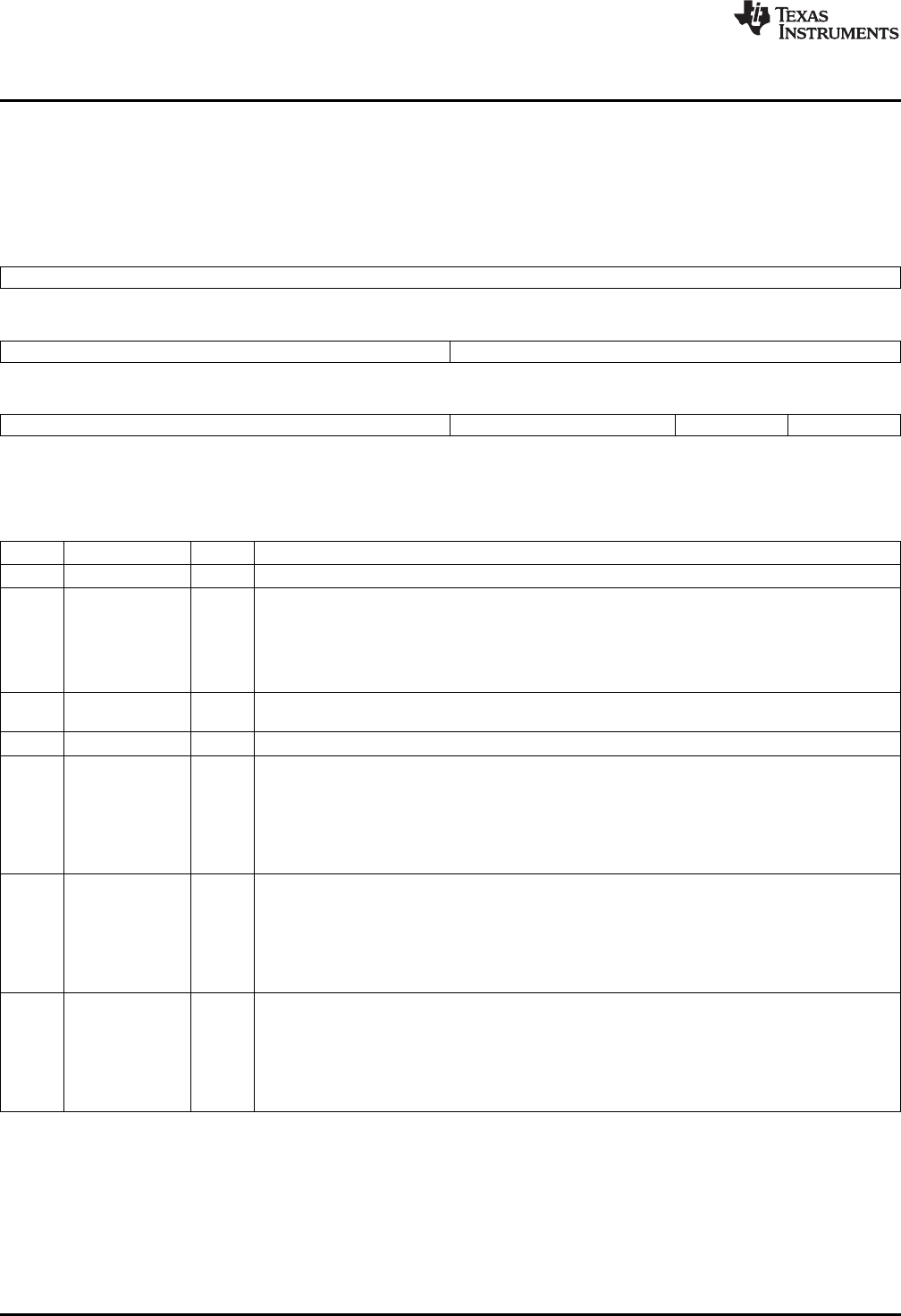

5.5 Timer Global Control Register (TGCR)

The timer global control register (TGCR) is shown in Figure 19 and described in Table 13. This register

contains a field for selecting the operating mode of the timer (TIMMODE), timer reset bits (TIMHIRS and

TIMLORS), and counters for TIMHI in the dual 32-bit timers unchained mode (TDDRHI and PSCHI).

Figure 19. Timer Global Control Register (TGCR)

31 16

Reserved

R/W-0

15 12 11 8

TDDRHI PSCHI

R/W-0 R/W-0

7 4 3 2 1 0

Reserved TIMMODE TIMHIRS TIMLORS

R-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 13. Timer Global Control Register (TGCR) Field Descriptions

Bit Field Value Description

31-16 Reserved Reserved. The reserved bit location is always read as 0. A value written to this field has no effect.

15-12 TDDRHI Timer divide-down ratio bits. This field is the prescale counter for TIMHI in the dual 32-bit timers

unchained mode (TIMMODE = 01b). When the timer is enabled, TDDRHI increments every timer

clock cycle. The timer counter (CNTHI) increments on the cycle after the TDDRHI matches the

value of PSCHI. TDDRHI resets to 0 and continues. If enabled one time, when CNTHI matches the

PRDHI, the timer stops; if the timer is enabled continuously, CNTHI resets to 0 on the cycle after

matching the PRDHI and the timer continues counting. The default value is 0000b.

11-8 PSCHI Prescale period bits. This field specifies the prescale period for TIMHI in the dual 32-bit timers

unchained mode (TIMMODE = 01b). The default value is 0000b.

7-4 Reserved Reserved. The reserved bit location is always read as 0. Read-only.

3-2 TIMMODE Timer mode bits determine the timer operating mode.

00b The timer is in the 64-bit general-purpose timer mode.

01b The timer is in the dual 32-bit timers unchained mode.

10b The timer is in the 64-bit watchdog timer mode.

11b The timer is in the dual 32-bit timers chained mode.

1 TIMHIRS TIMHI reset bit. Note that in order for the timer to function properly in 64-bit general-purpose timer

mode both the TIMHIRS and TIMLORS bits must be set to 1. If the timer is in the watchdog timer

active state, changing this bit does not affect the timer.

0 TIMHI is in reset. The TSTAT_HI bit of TCR is reset to 0. However, the counter register CNTHI

keeps its current value.

1 TIMHI is not in reset. TIMHI can be used as a 32-bit timer.

0 TIMLORS TIMLO reset bit. Note that in order for the timer to function properly in 64-bit general-purpose timer

mode both the TIMHIRS and TIMLORS bits must be set to 1. If the timer is in the watchdog timer

active state, changing this bit does not affect the timer.

0 TIMLO is in reset. The TSTAT_LO bit of TCR is reset to 0, and the timer output signal is in the

high-impedance state. However, the counter register CNTLO keeps its current value.

1 TIMLO is not in reset. TIMLO can be used as a 32-bit timer.

30

C6472/TCI648x 64-Bit Timer SPRU818B–December 2005–Revised September 2010

Submit Documentation Feedback

Copyright © 2005–2010, Texas Instruments Incorporated